www.czasopisma.pan.pl

BULLETIN OF THE POLISH ACADEMY OF SCIENCES TECHNICAL SCIENCES, Vol. 64, No. 3, 2016 DOI: 10.1515/bpasts-2016-0061

# Characterization of Al<sub>2</sub>O<sub>3</sub>/4H-SiC and Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/4H-SiC MOS structures

# A. TAUBE<sup>1,2\*</sup>, M. GUZIEWICZ<sup>1</sup>, K. KOSIEL<sup>1</sup>, K. GOŁASZEWSKA-MALEC<sup>1</sup>, K. KRÓL<sup>2</sup>, R. KRUSZKA<sup>1</sup>, E. KAMIŃSKA<sup>1</sup>, and A. PIOTROWSKA<sup>1</sup>

<sup>1</sup>Institute of Electron Technology, 32/46 Lotników Av., 02-668 Warsaw, Poland

<sup>2</sup>Institute of Microelectronics and Optoelectronics, Warsaw University of Technology, 75 Koszykowa St., 00-662 Warsaw, Poland

**Abstract.** The paper presents the results of characterization of MOS structures with aluminum oxide layer deposited by ALD method on silicon carbide substrates. The effect of the application of thin SiO<sub>2</sub> buffer layer on the electrical properties of the MOS structures with  $Al_2O_3$  layer has been examined. Critical electric field values at the level of 7.5–8 MV/cm were obtained. The use of 5 nm thick SiO<sub>2</sub> buffer layer caused a decrease in the leakage current of the gate by more than two decade of magnitude. Evaluated density of trap states near the conduction band of silicon carbide in  $Al_2O_3/4H$ -SiC MOS is about of  $1x10^{13} \text{ eV}^{-1}\text{ cm}^{-2}$ . In contrast, the density of the trap states in the  $Al_2O_3/SiO_2/4H$ -SiC structure is lower about of one decade of magnitude *i.e.*  $1x10^{12} \text{ eV}^{-1}\text{ cm}^{-2}$ . A remarkable change in the MOS structure is also a decrease of density of electron traps located deeply in the 4H-SiC conduction band below detection limit due to using of the SiO<sub>2</sub> buffer layer.

Key words: aluminum oxide, MOS, silicon carbide, 4H-SiC, high-ĸ dielectrics.

### 1. Introduction

Due to excellent material properties of silicon carbide, such as high value of critical electric field, high electron saturation velocity and thermal conductivity, silicon carbide semiconductor devices are now frequently used in power electronics [1]. From the perspective of application, power MOSFET transistors with breakdown voltage over 1 kV are particularly desirable. Electrical parameters of the new generation of silicon carbide MOSFETs are not yet satisfactory [2]. This problem results from the high density of interface traps at the dielectric-semiconductor interface, which are formed during high temperature oxidation of silicon carbide. This significantly deteriorates electron mobility in the channel, which rarely exceeds 100 cm<sup>2</sup>/Vs [3]. Simultaneously, within research on silicon carbide oxidation, works on applying high relative electric permittivity dielectrics (high- $\kappa$ ), such as hafnium oxide HfO<sub>2</sub>  $(\varepsilon_r = 15-25)$  or aluminum oxide Al<sub>2</sub>O<sub>3</sub>  $(\varepsilon_r = 8-11)$  [4] in silicon carbide MOSFET technology have been carried out recently. Aluminum oxide has higher energy band gap ( $E_{g} \sim 7 \text{ eV}$ ) as compared to other high-k dielectrics, which makes this material promising for application in 4H-SiC MOS power devices. However, due to relatively low value of barrier height between conduction bands of Al<sub>2</sub>O<sub>3</sub> and 4H-SiC ( $\phi_B \sim 1.5-1.6 \text{ eV}$ ), applying additional buffer layers is required to reduce gate leakage current markedly [5]. In addition, the buffer layer can also decrease the density of traps at dielectric-semiconductor interface [6]. In this work we present the results of the characterization of aluminum oxide layers grown by atomic layer deposition (ALD) method on 4H-SiC substrates, also on the substrate with thin  $SiO_2$  buffer layer deposited by plasma enhanced chemical vapor deposition (PECVD) [7].

#### 2. Experimental details

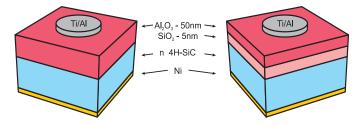

MOS structures used in this study were fabricated on low-resistivity 4H-SiC substrates  $(n \sim 5 \times 10^{18} \text{ cm}^{-3})$  with n-type  $(n \sim 5 \times 10^{15} \text{ cm}^{-3})$ , 10 µm thick epitaxial layer. Prior to the MOS fabrication the substrates were cleaned in organic solvents and dipped in 10% HF solution to remove the native oxide. The nickel layer was sputtered on the backside and annealed (Ar, 1050°C) to form an ohmic contact. Two kinds of samples were fabricated. On one part of samples, 5 nm SiO<sub>2</sub> buffer layer was fabricated by PECVD using SiH<sub>4</sub> and N<sub>2</sub>O plasma. Afterwards, a 50 nm layer of Al<sub>2</sub>O<sub>3</sub> was deposited on all samples by ALD. Al<sub>2</sub>O<sub>3</sub> layers were deposited at 200°C using trimethylaluminium (TMA) and water vapor (H<sub>2</sub>O) as Al and O precursors, respectively. Finally, a top layer of Ti/Al gate electrode ( $\varphi = 200 \ \mu m$ ) was deposited on top of Al<sub>2</sub>O<sub>3</sub> by sputtering and patterned by lift-off technique. A schematic sketch of fabricated Al<sub>2</sub>O<sub>3</sub>/4H-SiC and Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/4H-SiC structures is presented in Fig. 1.

Fig. 1. Scheme of fabricated Al\_2O\_3/4H-SiC and Al\_2O\_3/SiO\_2/4H-SiC MOS structures

\*e-mail: ataube@ite.waw.pl

A. Taube et al.

The surface morphology of aluminum oxide on 4H-SiC was examined by use of atomic force microscopy (AFM). Optical properties were determined using variable angle spectroscopic ellipsometry (VASE). Electrical characterization of fabricated MOS capacitors includes measurements of current-voltage (I–V) and capacitance-voltage (C–V) characteristics.

## 3. Results and discussion

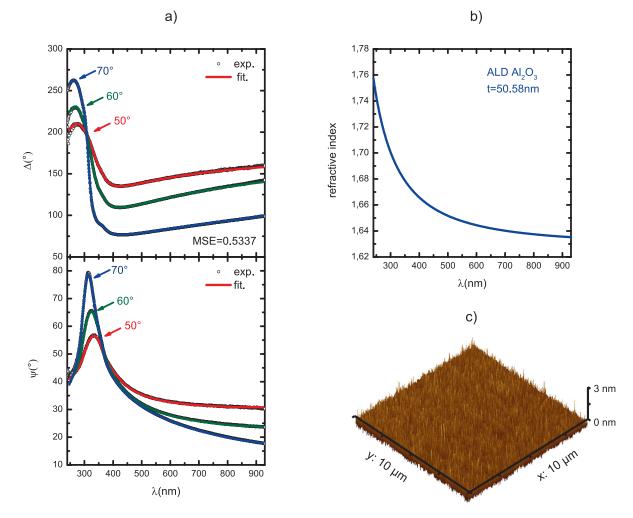

**3.1. Optical characterization and surface morphology.** Optical properties of  $Al_2O_3$  layer were determined by VASE. Optical parameters of the  $Al_2O_3$  film were modeled using Tauc-Lorentz dispersion model. An excellent fit of model parameters to experimental data was obtained (the mean squared error MSE was 0.53, Fig. 2a). Based on VASE analysis, the wavelength dependence of refractive index and extinction coefficient were determined (Fig. 2b). The extinction coefficient was equal zero in studied wavelength range. The refractive coefficient values are typical for amorphous  $Al_2O_3$  layers [8] and in 240–930 nm range it was decreasing approximately from 1.76 to 1.64. The

thickness of  $Al_2O_3$  film was determined to be 50.6 nm. Surface roughness (RMS) measured by means of AFM was about 0.46 nm, which indicates very good smoothness of ALD deposited  $Al_2O_3$  films (Fig. 2c).

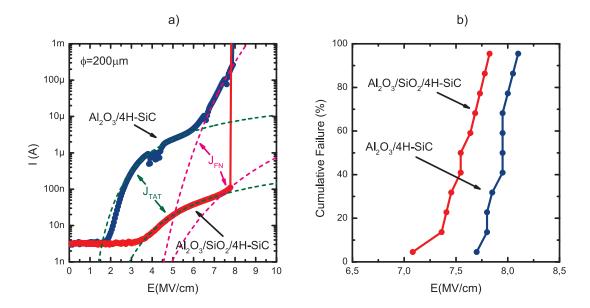

3.2. Electrical characterization. Figure 3 shows the measured current-voltage characteristics of Al<sub>2</sub>O<sub>3</sub>/4H-SiC and Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/4H-SiC MOS structures. As can be observed, the leakage current of MOS structures without SiO<sub>2</sub> buffer layer is greater than in the case of buffer layer. For electric field E within the values up to 2 MV/cm or up to 3MV/cm, the leakage current is below noise level of the measurement setup for the case without or with the SiO<sub>2</sub> buffer layer, respectively. For E = 5 MV/cm leakage current of Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/4H-SiC structures is over two orders of magnitude lower, and for E = 7.5 MV/cm over there orders of magnitude lower than in case of the Al<sub>2</sub>O<sub>3</sub>/4H-SiC structures. In comparison with hafnium oxide layers deposited by ALD on 4H-SiC, Al<sub>2</sub>O<sub>3</sub> layers deposited directly on 4H-SiC have much larger value of critical electric field ( $E_c = 4.5$  MV/cm for HfO<sub>2</sub>), which stems from the larger barrier height between conduction

Fig. 2. a) Dependence of ellipsometric angles  $\Psi$  and  $\Delta$ , b) the refractive index of  $Al_2O_3$  layers deposited by ALD method, c) an AFM image of the surface of the  $Al_2O_3$  film

www.czasopisma.pan.pl *Characterization of Al*<sub>2</sub>O<sub>3</sub>/4H-SiC and Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/4H-SiC MOS structures

Fig. 3. a) Current-voltage characteristics, b) distribution of electric breakdown probability of Al<sub>2</sub>O<sub>3</sub>/4H-SiC and Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/4H-SiC MOS structures

band of the dielectric and semiconductor. Similarly, for  $Al_2O_3/SiO_2$  gate stack the critical electric field is higher by approximately 1 MV/cm than in the case of HfO<sub>2</sub>/SiO<sub>2</sub> with the same buffer layer thickness [7].

Based on current-voltage characteristics, conduction mechanism of the leakage current in each of the structure was determined. For electric field E within the values up to about 6 MV/cm for  $Al_2O_3/4H$ -SiC and up to 7 MV/cm for  $Al_2O_3/SiO_2/4H$ -SiC structures the best fits to experimental data were obtained by using formula describing trap-assisted tunneling current ( $J_{TAT}$ ) [9]:

$$J_{TAT} = A \exp\left(\frac{-8\pi\sqrt{2qm^*}}{3hE}\varphi_t^{3/2}\right),\tag{1}$$

where A is constant, m<sup>\*</sup> is electron effective mass in Al<sub>2</sub>O<sub>3</sub>, h is Planck constant and  $\phi_T$  is trap energy level with regard to conduction band edge of the dielectric. The energy of traps in case of Al<sub>2</sub>O<sub>3</sub>/4H-SiC and Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/4H-SiC MOS structures was 0.38 and 0.46 eV. For electric field values above 6 MV/cm and 7 MV/cm, the dominant leakage current mechanism is tunneling through triangular barrier, i.e., tunneling in Folwer-Nordheim regime (J<sub>FN</sub>). The leakage current associated with Fowler-Nordheim tunneling is described by the following formula [9]:

$$J_{FN} = \frac{q^2}{8\pi h \varphi_B} E^2 \exp\left(\frac{-8\pi \sqrt{2qm^*}}{3hE} \varphi_B^{3/2}\right),$$

(2)

where q is elementary charge and  $\varphi_B$  is barrier height between conduction bands of dielectric and semiconductor. Determined  $\varphi_B$  values are 1.56 eV and 1.52 eV for the structures with and without SiO<sub>2</sub> buffer layer, respectively. These values are close to values for Al<sub>2</sub>O<sub>3</sub> and 4H-SiC reported in the literature [10]. Obtained critical electric field values were about 7.5–8 MV/cm. For the MOS structure without SiO<sub>2</sub> buffer layer  $E_c$  is slightly higher (0.5 MV/cm) than in the case with SiO<sub>2</sub> buffer layers. This might be altered by uncertainty of electric field values. However, quite similar critical electric field values indicate that electric breakdown occurs in the Al<sub>2</sub>O<sub>3</sub> layers for both type of structures.

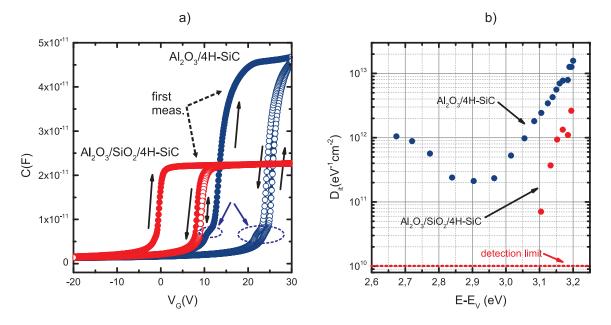

The C-V characteristics were measured at 1 MHz frequency. Due to the substantial shift of the measured C-V characteristics as a function of measuring voltage caused by the presence of significant charge in the gate stack or the high level of electrons trapped at the dielectric-semiconductor interface, we adopted the following methodology of measurements. The first measurement is made from accumulation to depletion and back. This step was preceded by a 5 minute voltage stress (-30 V) aiming at least partially discharge slow traps states and/or reduce the impact of mobile charge on the measured characteristics. From these measurements the energetic distribution of fast traps states near conduction band using Terman method [11] was extracted. Next, 5 min positive voltage stress (30 V) was performed and C-V characteristics were measured from accumulation to depletion and back. From shift of C-V curves measured under both conditions, the amount of slow states and fixed and mobile charge in the dielectric can be evaluated. Figure 4a shows measured C-V characteristics of Al<sub>2</sub>O<sub>3</sub>/4H-SiC and Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/4H-SiC MOS capacitors. Calculated relative dielectric constant of Al<sub>2</sub>O<sub>3</sub> was about 9. As follows from C-V measurements, the capacitor measured for the first time was characterized by relatively low flat band voltage. However, after voltage stress went into accumulation range, the flatband voltage was significantly shifted towards more positive values. This is due to trapping of carriers by high concentration of near interface traps. In case of the MOS structures with SiO<sub>2</sub> buffer layer this phenomenon is significant-

Fig. 4. a) Capacitance-voltage characteristics of Al<sub>2</sub>O<sub>3</sub>/4H-SiC and Al<sub>2</sub>O<sub>3</sub>/2H-SiC MOS structures, b) energy distribution of the density of surface states at dielectric-semiconductor interface based on capacitance-voltage characteristics

ly reduced. This indicates that trapping occurs in Al<sub>2</sub>O<sub>3</sub> layer, and the use of even 5 nm thick SiO<sub>2</sub> buffer layer decreases this phenomenon by moving the trapping centers from semiconductor surface. By analyzing the energetic distribution of traps states at the dielectric-semiconductor interface (Fig. 4b), it can be seen that in the case of Al<sub>2</sub>O<sub>3</sub>/4H-SiC structures the density of interface traps (D<sub>it</sub>) near the conduction band was about  $1.5 \times 10^{13} \text{ eV}^{-1} \text{ cm}^{-2}$  (for E-E<sub>v</sub> = 3.2 eV), and was almost an order of magnitude higher than in the case of Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/4H-SiC structures ( $D_{it} = 2.6 \times 10^{12} \text{ eV}^{-1} \text{ cm}^{-2}$ ,  $E - E_v = 3.2 \text{ eV}$ ). Moreover, in the case of structures with SiO<sub>2</sub> buffer layer, a rapid decrease of D<sub>it</sub> in function of the distance from the conduction band edge can be observed. For trap states with  $E-E_v$  located within up to 3.1 eV above the valence band edge, interface traps density falls below the detection limit of Terman method (~  $10^{10} \text{ eV}^{-1} \text{ cm}^{-2}$ ). In the case of  $Al_2O_3/4H$ -SiC MOS structures, the increase in the density of trap states located deeper in the band gap of 4H-SiC can be seen, which is manifested by increase of C-V characteristics (marked by circles in Fig. 4a). As compared to the literature data relating to Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/4H-SiC structures with a SiO<sub>2</sub> buffer layer formed by thermal oxidation of 4H-SiC [12], the Al<sub>2</sub>O<sub>3</sub> MOS structures with similar thickness of SiO<sub>2</sub> layer deposited by PECVD are characterized by much faster decrease of the density of interfaces traps located in the depth of the band gap of 4H-SiC. For Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> layers presented in [12], the density of interface states does not fall below 1×10<sup>12</sup> eV<sup>-1</sup>cm<sup>-2</sup> to 0.5 eV from conduction band edge.

# 4. Conclusions

The results of characterization of atomic layer deposited aluminum oxide on silicon carbide for MOS structures are presented. Fabricated MOS structures with and without thin SiO<sub>2</sub> buffer layer are characterized by very high critical electric field values in range 7.5, 8 MV/cm. The use of 5 nm thick SiO<sub>2</sub> buffer layer causes decrease of gate leakage current by at least two-orders of magnitude in comparison to Al<sub>2</sub>O<sub>3</sub> layers on bare 4H-SiC. Analysis of C–V measurements related to the dielectric-semiconductor interface shown that by the application of the (5 nm) SiO<sub>2</sub> buffer layer interface traps density near conduction band of 4H-SiC can be decreased almost by an order of magnitude from  $1 \times 10^{13}$  to  $1 \times 10^{12} \text{eV}^{-1} \text{ cm}^{-2}$ . Moreover, the density of traps located deeper in the 4H-SiC bandgap decreased below  $1 \times 10^{10} \text{eV}^{-1} \text{ cm}^{-2}$ , i.e. the value undetectable by Terman method applied in this work.

Acknowledgments. The research was partially supported by the European Union within European Regional Development Fund through an Innovative Economy grant (POIG.01.03.01–00–159/08, InTechFun). Andrzej Taube was supported by the European Union in the framework of European Social Fund through the Warsaw University of Technology Development Programme.

# References

- M. Levinshtein, S. Rumyantsev and M. Shur, Handbook Series on Semiconductor Parameters: Volume 2: Ternary And Quaternary III-V Compounds, World Scientific, London, 1996, 1999.

- [2] B.J. Baliga., Silicon Carbide Power Devices, World Scientific, Singapore, 2006.

- [3] D. Okamoto, H. Yano, K. Hirata, T. Hatayama and T. Fuyuki, "Improved inversion channel mobility in 4H-SiC MOSFETs on Si face utilizing phosphorus-doped gate oxide", *IEEE Elec. Dev. Let.*, 31(7), 710–712 (2010).

- [4] J. Robertson, "High dielectric constant gate oxides for metal oxide Si transistors", *Rep. Prog. Phys.* 69, 327–396 (2006).

- [5] K.Y. Cheong, J.H. Moon, H.J. Kim, W. Bahng and N.K. Kim, "Analysis of current conduction mechanisms in atomic-layer-deposited Al<sub>2</sub>O<sub>3</sub> gate on 4H silicon carbide", *App. Phys. Let.* 90, 162113 (2007).

- [6] K.Y. Cheong, J.H. Moon, T.J. Park, J.H. Kim, C.S. Hwang, H.J. Kim, W. Bahng and N.K. Kim, "Improved electronic performance of HfO<sub>2</sub>/SiO<sub>2</sub> stacking gate dielectric on 4H SiC", *IEEE Tran. on Elec. Dev.* 54(12), 3409–3413 (2007).

- [7] A. Taube, K. Korwin-Mikke, T. Gutt, T. Małachowski, I. Pasternak, M. Wzorek, A. Łaszcz, M. Płuska, W. Rzodkiewicz, A. Piotrowska, S. Gierałtowska, M. Sochacki, R. Mroczyński, E. Dynowska and J. Szmidt, "Fabrication and characterization of hafnium oxide thin layers for application in silicon carbide MOSFET technology", *Elektronika*, 52(9), 117–120 (2011).

- [8] M.D. Groner, F.H. Fabreguette J.W. Elam and S.M. George, "Low-temperature Al<sub>2</sub>O<sub>3</sub> atomic layer deposition", *Chem. Mater.* 16, 639–645 (2004).

- [9] Y. Seo, S. Lee, I. An, C. Song, and H. Jeong, "Conduction mechanism of leakage current due to the traps in ZrO<sub>2</sub> thin film", *Semicond. Sci. Technol.* 24, 115016 (2009).

- [10] C.M. Tanner, Y.Ch. Perng, C. Frewin, S.E. Saddow and J.P. Chang, "Electrical performance of Al<sub>2</sub>O<sub>3</sub> gate dielectric films deposited by atomic layer deposition on 4H-SiC", *App. Phys. Let.* 91, 203510 (2007).

- [11] L.M. Terman, "An investigation of surface states at a silicon/ silicon oxide interface employing metal-oxide-silicon diodes", *Solid-State Electron.* 5, 285 (1962).

- [12] K.Y. Cheong, J.H. Moon, D. Eom, H.J. Kim, W. Bahng, and N-K. Kim, "Electronic properties of atomic-layer-deposited Al<sub>2</sub>O<sub>3</sub>/thermal-nitrided SiO<sub>2</sub> stacking dielectric on 4H SiC", *Electrochem. Solid-State Lett.*, 10(2), H69-H71 (2007).