DOI 10.24425/aee.2025.154989

# Nearest level control for improving total harmonic distortion in a 13-level three-phase multilevel inverter

MD SHOWKOT HOSSAIN <sup>101,2</sup>, MD AKIB HASAN <sup>103</sup>, NURUL AIN MOHD SAID <sup>101,2</sup>, WAHIDAH ABD HALIM <sup>101,2</sup>, AUZANI JIDIN <sup>101,2</sup>

<sup>1</sup>Faculty of Electrical Technology and Engineering, Universiti Teknikal Malaysia Melaka Melaka, 76100, Malaysia

<sup>2</sup>Power Electronics and Drive Research Group, Universiti Teknikal Malaysia Melaka Melaka, 76100 Malaysia

<sup>3</sup> Faculty of Electrical Engineering & Technology, Universiti Malaysia Perlis Perlis, 02100, Malaysia

> e-mail: {hossain33-2682/hasan33-2718}@diu.edu.bd, {⊠ nurulain/wahidahhalim/auzani}@utem.edu.my

(Received: 12.12.2024, revised: 25.08.2025)

Abstract: This research investigates the application of nearest level control (NLC) in a three-phase transistor-clamped H-bridge (TCHB) multilevel inverter (MLI) to enhance power quality and reduce harmonic distortion. The TCHB topology offers high performance with fewer components compared to traditional MLI configurations, making it particularly suitable for renewable energy applications. By operating at fundamental switching frequency, the NLC technique effectively minimizes switching losses while reducing total harmonic distortion (THD). The study includes MATLAB/Simulink-based simulation modeling and experimental validation using dSPACE, tested under varying load conditions. For a 13-level TCHB inverter with equal DC supplies and a modulation index of M = 1, the voltage THD was 5.22% (resistive load) and 5.17% (inductive-resistive load) in simulations, which was further reduced to 4.5% and 4.2% in experiments. The NLC technique demonstrated superior harmonic performance and efficiency compared to conventional methods, particularly at higher voltage levels. This study highlights the practical advantages of the TCHB inverter, including reduced component count, simplified control implementation, and enhanced output waveform quality. These findings confirm the potential of the NLC-based TCHB inverter for high-performance motor drives and grid-tied renewable energy systems, positioning it as a promising solution for modern power electronics applications.

**Key words:** harmonic minimization, multilevel inverter, nearest level control, renewable energy, total harmonic distortion, TCHB MLI

## 1. Introduction

The expansion of renewable energy sources, electric cars, and industrial applications has led to a large increase in demand for power electronic systems with high power, high efficiency, and low harmonic distortion in recent years [1–5]. Multilevel inverters have emerged as a promising solution to address these demands by offering improved performance characteristics compared to conventional two-level inverters [6]. Multilevel inverters utilize multiple levels of DC voltage to synthesize an AC output waveform, thereby reducing harmonic distortion, minimizing voltage stress on power semiconductors, and enhancing system efficiency [7, 8]. This technology has attracted considerable interest from researchers and industry experts, resulting in the creation of several multilevel inverter structures and modulation techniques [9, 10].

Among the primary multilevel inverter topologies are the neutral-point-clamped (NPC), flying capacitor (FC), and cascaded H-bridge (CHB) inverters [11]. The NPC inverter, characterized by its ability to mitigate common-mode voltage issues and reduce switching losses, has found extensive application in medium to high-power grid-connected systems [12]. On the other hand, FC inverters, known for their simplicity and reduced component count, are often employed in low to medium-power applications such as renewable energy systems and motor drives [13]. Meanwhile, CHB inverters, with their scalability and fault-tolerance operation, are widely utilized in high-voltage applications including electric vehicles and high-power motor drives [14]. Additionally, emerging topologies like Transistor-Clamped H-Bridge (TCHB) offer further advancements in performance and flexibility. The TCHB topology, which combines carrier-based modulation with H-Bridge cells, improves harmonic performance and voltage quality, making it well-suited for high-power grid-connected applications [15].

Modulation techniques are essential for shaping the output waveform of multilevel inverters, significantly influencing their harmonic performance, and switching losses. Among these, pulse width modulation (PWM) is commonly employed, where the pulse width dictates the amplitude of the output voltage. PWM ensures precise control of the output voltage and effectively reduces harmonic distortion [16, 17]. Another advanced method, space vector pulse width modulation (SVPWM), optimally utilizes the available voltage vectors, resulting in reduced harmonic content and improved efficiency [18]. Selective harmonic elimination (SHE) aims to eliminate specific harmonics by solving nonlinear equations, offering superior harmonic performance at the expense of increased computational complexity [19, 20]. Techniques like nearest vector control (NVC) and nearest level control (NLC) are designed to mitigate specific harmonics by introducing notches in the output voltage waveform, thus enhancing harmonic suppression capabilities [21]. High switching frequency (HSF) modulation methods, including PWM and SVPWM, offer better harmonic performance but may incur higher switching losses due to increased switching frequency [22,23]. Conversely, low switching frequency modulation techniques like SHE, NVC, and NLC can reduce switching losses but may lead to higher harmonic distortion [24]. Therefore, the selection of modulation technique and switching frequency depends on the specific requirements of the application, balancing harmonic performance and switching losses to achieve optimal system efficiency and reliability.

Harmonics are a critical factor influencing the performance and efficiency of power converters, particularly in multilevel inverter systems [25, 26]. The presence of harmonics in any electrical system poses significant risks, including overheating, losses, reduced performance, and shortened

service life of electrical components. Therefore, minimizing harmonics is a critical objective to mitigate these issues effectively. Harmonics refer to the presence of frequency components that are integer multiples of the fundamental frequency, causing distortions in output voltage waveform. These harmonics can cause various detrimental effects, including increased losses, electromagnetic interference, and reduced system efficiency. total harmonic distortion (THD) is a quantitative measure used to assess the level of harmonic distortion in the output waveform relative to the fundamental frequency [27, 28]. In multilevel inverters, the presence of multiple voltage levels and switching states offers inherent advantages in mitigating harmonics compared to traditional two-level inverters. However, careful design and selection of modulation techniques are crucial to further minimize harmonic distortion and enhance system performance [29]. Additionally, advancements in control strategies and modulation techniques continue to play a significant role in improving harmonic performance and overall system efficiency in multilevel converter applications [30, 31].

This study focuses on the TCHB MLI, a topology that achieves high power quality with fewer electronic components compared to conventional MLIs. The key novelty lies in utilizing the NLC method to optimize THD reduction and switching loss minimization. Unlike traditional modulation techniques, NLC achieves a balance between efficiency and harmonic suppression without introducing computational complexity. Additionally, the symmetrical configuration of the TCHB inverter further enhances waveform quality, producing an output that closely approximates a sinusoidal waveform.

A comprehensive performance analysis is conducted, comparing the proposed method with existing literature to highlight its advantages in THD reduction and efficiency improvement. This research contributes to advancing power electronic systems by addressing key challenges in multilevel inverter modulation and renewable energy integration.

## 2. The TCHB inverter and its modulation

A three-phase 13-level TCHB MLI and its control technique (NLC) are modeled through simulation using MATLAB/Simulink.

## 2.1. Adopted 13-level TCHB MLI

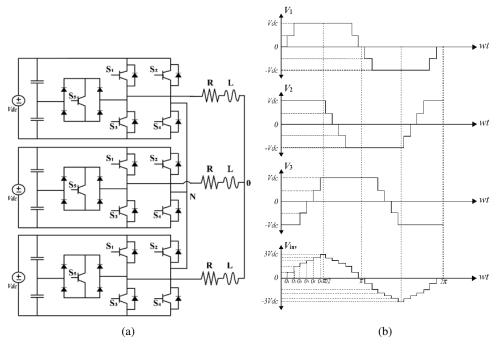

The three-phase 13-level TCHB inverter configuration is shown in Fig. 1(a). This configuration consists of three identical TCHB cells, each powered by an equal DC voltage supply. As shown, the configuration employs fifteen switches and twelve diodes to produce a 13-level output voltage. Each TCHB cell operates with an input voltage of 60 V, while the DC-link capacitors have uniform capacitances of 2200  $\mu$ F. Table 1 summarizes the specification used for the simulation parameters for the TCHB MLI. The switching state of the TCHB inverter are given in Table 2, where active switches are on state of the switches during each level generation. By adding three cascaded TCHB cells  $(v_1, v_2, v_3)$ , the 13-level output  $(v_{inv})$  is formed as in Eq. (1).

$$v_{\text{inv}} = v_1 + v_2 + v_3. \tag{1}$$

656

Fig. 1. Three-phase 13-level TCHB MLI: (a) circuit diagram; (b) output waveform generation

Table 1. Summarizes the specification used for the simulation parameters for the TCHB MLI

| Parameters                 | Values  |

|----------------------------|---------|

| DC supply for cell-1, 2, 3 | 60 V    |

| Load resistance            | 100 Ω   |

| DC-link capacitor          | 2200 μF |

| Load inductance            | 18.4 mH |

| Fundamental frequency      | 50 Hz   |

Table 2. Switching state for proposed 13-level TCHB MLI

| No. of level | Active switches (on state)                                                                                | $V_{ m inv}$         |

|--------------|-----------------------------------------------------------------------------------------------------------|----------------------|

| 1            | $S_{11}, S_{14}, S_{21}, S_{24}, S_{31}, S_{34}$                                                          | $3V_{\rm dc}$        |

| 2            | $S_{11}, S_{14}, S_{21}, S_{24}, S_{34}, S_{35}$                                                          | $2.5V_{\mathrm{dc}}$ |

| 3            | S <sub>11</sub> , S <sub>14</sub> , S <sub>24</sub> , S <sub>25</sub> , S <sub>34</sub> , S <sub>35</sub> | $2V_{\mathrm{dc}}$   |

| 4            | $S_{14}, S_{15}, S_{24}, S_{25}, S_{34}, S_{35}$                                                          | $1.5V_{\mathrm{dc}}$ |

| 5            | S <sub>14</sub> , S <sub>15</sub> , S <sub>24</sub> , S <sub>25</sub> , S <sub>33</sub> , S <sub>34</sub> | $V_{ m dc}$          |

| 6            | S <sub>14</sub> , S <sub>15</sub> , S <sub>23</sub> , S <sub>24</sub> , S <sub>33</sub> , S <sub>34</sub> | $0.5V_{\mathrm{dc}}$ |

Continued on next page

| racie 2 Communea from previous page |                                                                                                           |                       |  |  |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------|--|--|

| No. of level                        | Active switches (on state)                                                                                | Vinv                  |  |  |

|                                     | S <sub>13</sub> , S <sub>14</sub> , S <sub>23</sub> , S <sub>24</sub> , S <sub>33</sub> , S <sub>34</sub> |                       |  |  |

| 7                                   | or                                                                                                        | 0                     |  |  |

|                                     | $S_{11}, S_{12}, S_{21}, S_{22}, S_{31}, S_{32}$                                                          |                       |  |  |

| 8                                   | $S_{12}, S_{15}, S_{21}, S_{22}, S_{31}, S_{32}$                                                          | $-0.5V_{\mathrm{dc}}$ |  |  |

| 9                                   | $S_{12}, S_{15}, S_{22}, S_{25}, S_{31}, S_{32}$                                                          | $-V_{ m dc}$          |  |  |

| 10                                  | $S_{12}, S_{15}, S_{22}, S_{25}, S_{32}, S_{35}$                                                          | $-1.5V_{\mathrm{dc}}$ |  |  |

| 11                                  | $S_{12}, S_{13}, S_{22}, S_{25}, S_{32}, S_{35}$                                                          | $-2V_{\rm dc}$        |  |  |

| 12                                  | $S_{12}, S_{13}, S_{22}, S_{23}, S_{32}, S_{35}$                                                          | $-2.5V_{\mathrm{dc}}$ |  |  |

| 13                                  | $S_{12}, S_{13}, S_{22}, S_{23}, S_{31}, S_{33}$                                                          | $-3V_{\rm dc}$        |  |  |

|                                     |                                                                                                           |                       |  |  |

Table 2 – Continued from previous page

Figure 1(b) depicts the voltage output waveforms generated by cell-1, cell-2, and cell-3 for the 13-level inverter. The 13-level output of the TCHB inverter is achieved by combining the individual voltages of the three TCHB cells.

### 2.2. Nearest level control technique

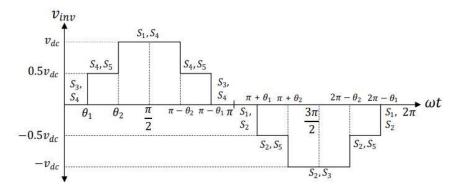

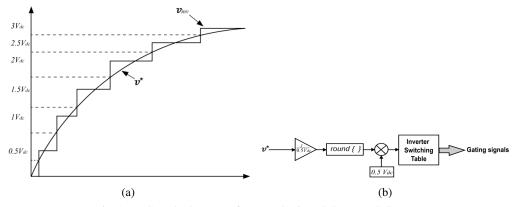

The application of the NLC technique for the 13-level TCHB inverter is depicted in Fig. 3. The principle involves comparing the reference signal with the desired voltage levels. Initially, the output remains at zero until the first switching angle is reached. The output transitions to  $0.5v_{\rm dc}$  when the reference signal reaches or exceeds  $0.25v_{\rm dc}$  and maintains this level until the reference surpasses  $0.75v_{\rm dc}$ . At this point, the output switches to  $v_{\rm dc}$ . This process continues sequentially to achieve all desired output levels. With each step of the TCHB inverter corresponding to  $0.5v_{\rm dc}$ , the maximum approximation error is limited to  $0.25v_{\rm dc}$ , as illustrated in Fig. 3(a).

The control logic of the NLC method for TCHB inverter is illustrated in Fig. 3(b). The nearest voltage level can be obtained by:

$$v_{\text{inv}} = 0.5v_{\text{dc}} * \text{round}_{0.5} \left\{ \frac{v^*}{0.5v_{\text{dc}}} \right\}.$$

(2)

The nearest round function is defined such that round  $\{x\}$  is the integer closest to x. To resolve ambiguity for half-integers, the convention is that half-integers are always rounded to the nearest even number [32]. For example, round  $\{1.4\} = 1$ , round  $\{1.5\} = 2$ , round  $\{1.6\} = 2$  as well and so on.

The switching angles for any number of levels using the NLC method are determined by the following equation:

$$\theta_i = \sin^{-1}\left(\frac{i - 0.5}{x}\right),\tag{3}$$

where  $i = 1, 2, ..., \frac{n-1}{2}$ , n is the number of levels and  $x = \frac{n-1}{2}$ .

As the number of levels increases, the switching angles  $\theta_i$  become closer to each other, resulting in a waveform that closely approximates a sinusoidal shape.

For a symmetrical TCHB inverter, the modulation index M is calculated using:

$$M = \frac{V_{\text{ref}}}{s * 0.5 v_{\text{dc}}},\tag{4}$$

where s is the step number in a quarter wave, and  $V_{\text{ref}}$  is the amplitude of the reference.

The waveform of the inverter's output voltage is depicted in Fig. 2, with the intervals for switch activation illustrated within the same figure. A single cycle of the TCHB output waveform is divided into six distinct regions, as detailed in Table 3.

Fig. 2. Five-level TCHB inverter output voltage waveform

Fig. 3. NLC method (a) waveform synthesis and (b) control diagram

To avoid the risk of a short circuit fault across the DC voltage source, switches  $S_1$  and  $S_3$  or  $S_2$  and  $S_4$  (the switches within one leg of the H-bridge) should not be simultaneously activated.

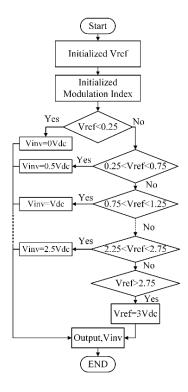

The process of flow diagram of NLC technique is shown in Fig. 4. The flowchart illustrates the NLC technique for determining the output voltage ( $\nu_{inv}$ ) of a multilevel inverter. The process begins by initializing the reference voltage ( $\nu^*$ ) and the DC voltage step size ( $0.5\nu_{dc}$ ). The system compares the reference voltage to predefined thresholds to select the appropriate output level. For instance, if  $\nu^*$  is less than  $0.25\nu_{dc}$ , the output is set to  $0\nu_{dc}$ , if it lies between  $0.25\nu_{dc}$  and  $0.75\nu_{dc}$ , the output is  $0.5\nu_{dc}$ ; and if it exceeds  $0.75\nu_{dc}$ , the output switches to  $\nu_{dc}$ . This comparison

| Region | Interval                                                                                              | ON switches                                                           | Voltage level                 |

|--------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------|

| 1      | $0 \le \omega t \le \theta_1 \text{ and } \pi - \theta_1 \le \omega t \le \pi$                        | $S_1, S_2 \text{ (or } S_3, S_4)$                                     | 0                             |

| 2      | $\theta_1 \le \omega t \le \text{and } \pi - \theta_2 \le \omega t \le \pi - \theta_1$                | $S_1, S_4$                                                            | +V <sub>dc</sub>              |

| 3      | $\theta_2 \le \omega t \le \pi - \theta_2$                                                            | S <sub>4</sub> , S <sub>5</sub>                                       | $+\frac{1}{2}V_{dc}$          |

| 4      | $\pi \le \omega t \le \pi + \theta_1 \text{ and } 2\pi - \theta_1 \le \omega t \le 2\pi$              | S <sub>1</sub> , S <sub>2</sub> (or S <sub>3</sub> , S <sub>4</sub> ) | 0                             |

| 5      | $\pi + \theta_1$ $\omega t \le \pi + \theta_2$ and $2\pi - \theta_2 \le \omega t \le 2\pi - \theta_1$ | $S_2, S_5$                                                            | $-\frac{1}{2}V_{\mathrm{dc}}$ |

| 6      | $\pi + \theta_2 \le \omega t \le 2\pi - \theta_2$                                                     | $S_2, S_3$                                                            | $-V_{ m dc}$                  |

Table 3. Regions of one output cycle of the TCHB inverter

continues for all levels to minimize the error between  $v^*$  and  $v_{inv}$ . The iterative process ensures that the reference voltage is matched to the nearest voltage level, with the output voltage updated accordingly. The final output voltage is then applied to the inverter, ensuring efficient and accurate voltage control with minimal error.

Fig. 4. NLC technique output generation flow diagram

The primary advantage of the NLC technique lies in its simplicity in concept, easy implementation, and better efficiency. However, its main drawback is its reduced effectiveness when dealing with a smaller number of levels, as the approximation error becomes more significant [33].

## 3. Simulation and experimental results

This section provides simulation and experimental results for the 13-level TCHB multilevel inverter. It starts with simulation results using R loads and then extends to RL loads. Output results for simulation and experiments show the inverter phase voltage and phase current. The comparison between simulation and experimental findings is carried out to confirm the effectiveness of the proposed topology and its control strategy. Additionally, the selection of parameters such as DC supply voltage, inductance, and capacitance for both simulation and experimental setups is based on previous research on TCHB inverters [34], ensuring optimal performance. This approach simplifies the component selection process, leading to improved efficiency, stability, and harmonic reduction in the system.

## 3.1. Simulation results

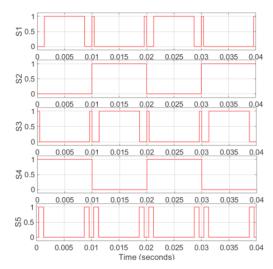

This section presents the simulation results of a 13-level TCHB multilevel inverter. The model of this simulation was explained in the previous Section 2. As mentioned earlier, all three TCHB cells are powered by 60 V DC supply, the gate pulse for the switches  $(S_1 \text{ to } S_5)$  for all three TCHB cells are shown in Fig. 5.

Fig. 5. Gate pulse for switches S<sub>1</sub> to S<sub>5</sub>

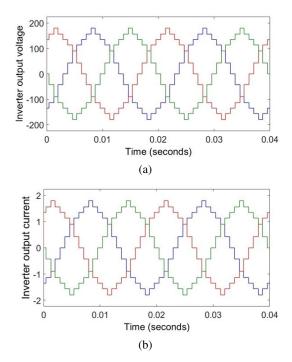

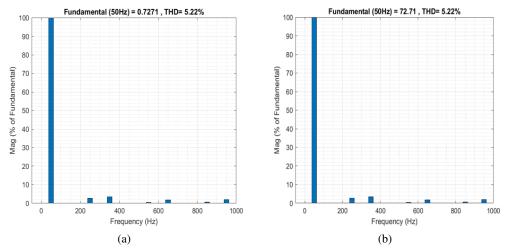

For better understanding to make the calculation easier, the modulation index is considered as M=1, so according to Eq. (4), it can be concluded ratio between the reference amplitude  $V_{\rm ref}$  and sum of the DC voltage supply is equal to 1. The output voltage and current waveform of the inverter is shown in Fig. 6. Voltage and current THD at M=1, using R load (R = 100  $\Omega$ ) are illustrated in Fig. 7. The voltage and current THD of 5.22% was obtained from the simulation using R load. The voltage and current THD is similar due to the use of R load, resistance alone does not affect the current waveform in terms of shape.

Fig. 6. Output waveform at M = 1, using R load: (a) voltage; (b) current

Fig. 7. Output THD at M = 1, using R load: (a) voltage; (b) current

The results are also tested using RL load (R = 100  $\Omega$  and L = 20 mH). As the RL load acts like a filter, it makes the output closer to the sinusoidal. Figure 8 presents the output voltage and current waveforms of the inverter, while Fig. 9 illustrates the voltage and current THD for M=1. The voltage and current THD of 5.17% and 4.52% was obtained from the simulation using RL load. If a larger inductance is used, the current waveform becomes approximately sinusoidal.

Fig. 8. Output waveform at M = 1, using RL load: (a) voltage; (b) current

Fig. 9. Output THD at M = 1, using RL load: (a) voltage and (b) current

## 3.2. Experimental results

This section presents the experimental results of the 13-level TCHB multilevel inverter. The output voltage and current waveforms are captured using a Tektronix TDS 2024C Oscilloscope, while a Fluke 435 power quality analyzer was employed to measure the voltage and current THDs as

well as individual harmonic components. Results are examined using both R and RL load explained earlier. The experimental setup utilizes the dSPACE DS1003 real-time control platform, which is responsible for implementing the NLC technique for the inverter. It is programmed using MAT-LAB/Simulink and ControlDesk, enabling real-time tuning and monitoring of inverter performance.

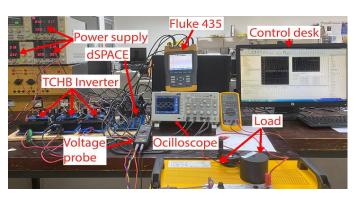

Table 4 outlines the system parameters and components used in the experimental setup and hardware prototype. Figure 10 illustrates the experimental setup, highlighting the power supply, dSPACE, inverter circuit with gate drives, load and measuring instruments are shown.

| Parameters            | Values    |

|-----------------------|-----------|

| Number of cells       | 3         |

| IGBT module           | IRGP4062D |

| DC-link capacitor     | 2 200 μF  |

| DC link diode         | RURG8060  |

| Fundamental frequency | 50 Hz     |

| Load resistance       | 100 Ω     |

Table 4. System parameters and components used in the experimental setup

18.4 mH

3 µsec

Load inductance

Dead band\*

Fig. 10. Experimental setup of the system including inverter prototype

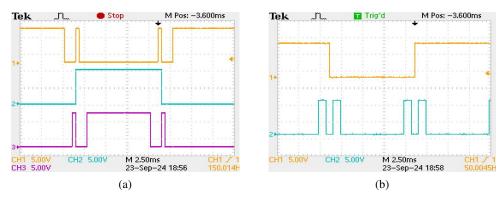

The gate signals for the switches of cell-1  $(S_{11} - S_{51})$ , cell-2  $(S_{12} - S_{52})$ , and cell-3  $(S_{13} - S_{53})$  of the 13- level TCHB MLI are shown in Fig. 11(a) and 11(b). These gate signals are similar to the simulation results.

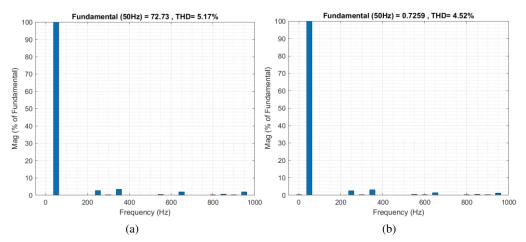

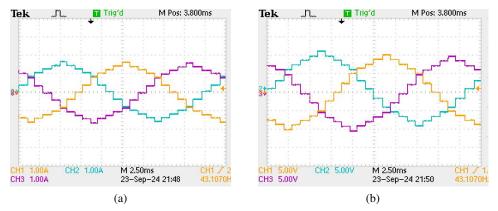

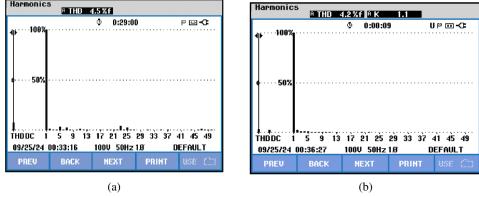

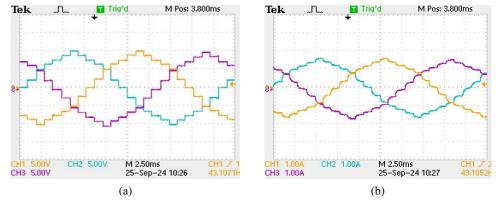

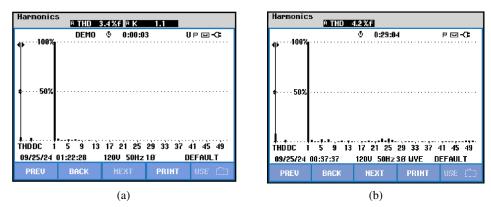

Figure 12(a) and 12(b) shows the voltage and current waveforms for 13-level TCHB multilevel inverter using R load at M = 1. Both voltage and current THD are 4.5% and 4.2%, as shown in Fig. 13(a) and 13(b), respectively.

<sup>\*(</sup>Between the gate pulse of two IGBTs in the same leg)

Fig. 11. Gate signals for the IGBT switches: (a) switches  $S_1$ ,  $S_2$  and  $S_3$ , and (b) switches  $S_4$  and  $S_5$

Fig. 12. Experimental results using R load at M = 1: (a) output voltage; (b) output current

Fig. 13. Experimental results using R load at M = 1: (a) voltage THD; (b) current THD

The results using RL load also verified using the experiment. Inverter output voltage and current waveforms shown in Fig. 14(a) and 14(b) respectively at M=1. Both voltage and current THD are 4.2% and 3.4%, as can be seen in Fig. 15(a) and 15(b), respectively.

Fig. 14. Experimental results using RL load at M = 1: (a) output voltage; (b) output current

Fig. 15. Experimental results using R load at M = 1: (a) voltage THD; (b) current THD

## 4. Results and discussion

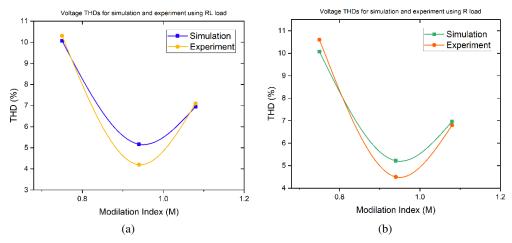

The results from simulation and experiments have been carried out using R and RL load. The voltage and current THD from both simulation and experiments are very close with a slight deviation. The voltage and current THDs from modeling and experimental results utilizing R and RL loads for various modulation indices are displayed in Table 5 and Fig. 16. THD was calculated up to the 20th harmonic order (N=20) with a maximum frequency of 1000 Hz in both MATLAB simulation and experimental measurements using the Fluke 435 power analyzer. This ensures consistency between simulation and experiment while capturing all significant harmonics affecting power quality.

For values of the modulation index M below 0.75, the output waveform reduces to a 9-level structure, resulting in a significant increase in THD. Similarly, when M exceeds 1.08, THD begins to rise again, even though the number of output levels remains unchanged. To present the most meaningful results and provide clarity on system performance, we have therefore focused on reporting the outcomes specifically for M = 0.75 and M = 1.08, excluding other values aside from M = 1.0. This allows for a clearer understanding of the critical behaviors within this operating range.

| Parameters       |            | THD (v) |      |      | THD (i) |      |      |

|------------------|------------|---------|------|------|---------|------|------|

| Modulation index |            | 0.75    | 1    | 1.08 | 0.75    | 1    | 1.08 |

| R load           | Simulation | 10.07   | 5.22 | 6.79 | 10.08   | 5.22 | 6.97 |

|                  | Experiment | 10.6    | 4.5  | 6.8  | 10.3    | 4.2  | 6.6  |

| RL load          | Simulation | 10.07   | 5.17 | 6.95 | 7.69    | 4.52 | 6.6  |

|                  | Experiment | 10.3    | 4.2  | 7.1  | 7.3     | 3.4  | 6.4  |

Table 5. Summary of the simulation and experimental results

Fig. 16. THD comparison of inverter for simulation and experiment using different modulation index: (a) using R load and (b) using RL load

The THD from simulation using R load shows the same value, however in the experiments results it slightly different. As RL load acts as a filter, it makes the current waveform more sinusoidal and using RL load significantly improve the current THD. The simulation results are in good agreement with the experimental results in both loads conditions.

It can be seen that, unlike the voltage THD, current THD in experiments is lower than the that in simulation for both R and RL load. This slight occurs due to the measurement equipment's that is used, like current prove filters some current, thus reducing the THD in the experiments.

The comparison between simulation and experimental results shows strong consistency, affirming the effectiveness of the NLC method in minimizing harmonics for the chosen MLI topology. As demonstrated in the figures, THD increases when the modulation index is reduced, resulting in a lower number of output voltage levels. Similarly, when the modulation index exceeds its optimal value, the THD rises again, even though the system retains 13 output voltage levels. These findings reinforce the importance of selecting an appropriate modulation index for balancing THD reduction and maintaining adequate output levels in the inverter system.

Although this study focuses on the 13-level TCHB inverter, the principles of THD reduction and efficiency improvement using NLC are applicable to TCHB inverters with varying levels. Increasing the number of levels in a TCHB inverter generally leads to better waveform quality and lower harmonic distortion, making NLC a suitable modulation strategy for higher-level configurations (e.g., 17-level, 21-level). However, scaling up introduces challenges such as control complexity and increased switching components, which should be explored in future work.

## 4.1. Comparison with relevant literature studies

This research assesses the performance of the proposed NLC method implemented in a three-phase TCHB inverter compared to other methods existing in the literature. The comparison focuses on two main performance metrics, THD and the number of levels generated to demonstrate how the NLC method enhances system efficiency and power quality. Table 6 summarizes the benefits of NLC in achieving superior performance in THD reduction, efficient power quality. The NLC technique offers significant advantages over PWM, SVPWM, and SHE by achieving a THD of 4.73% while reducing switching losses by 30–50%, leading to improved efficiency and thermal performance [35]. Unlike high-frequency PWM and SVPWM, NLC operates at a lower switching frequency, minimizing stress on power semiconductor devices and extending hardware lifespan. Additionally, NLC eliminates the need for complex nonlinear equations required in SHE, simplifying implementation and reducing computational burden on controllers. Its scalability allows seamless integration into various multilevel inverter topologies, making it an optimal choice for high-power applications such as electric vehicles, industrial motor drives, and grid-connected renewable energy systems [36].

Table 6. Summary of recent modulation technique applied to TCHB MLI

| Modulation technique            | Inverter type | THD (%) | Observations                                                                                        |

|---------------------------------|---------------|---------|-----------------------------------------------------------------------------------------------------|

| SHE [37]                        | 13-Level TCHB | 6.77%   | Effective in narrow range but THD increases outside narrow modulation range                         |

| CBPWM [25]                      | 5-Level TCHB  | 29.17%  | Higher THD compared to SVPWM, which offers better performance                                       |

| SVPWM [25]                      | 5-Level TCHB  | 13.12%  | Improved THD reduction over CBPWM                                                                   |

| PDPWM [38]                      | 9-Level TCHB  | 9.3%    | Achieved with 30 switches; moderately high THD                                                      |

| MPC [39]                        | 13-Level TCHB | 10.22%  | Though it uses 15 switches for 13-level, it still has high voltage THD.                             |

| ANN-based modulation [40]       | 5-Level TCHB  | 14.48%  | ANN technique provides lower THD content at output compared with PSO technique, but higher than NLC |

| NLC [36,41,42] (adopted method) | 13-Level TCHB | 4.73%   | NLC maintains low THD across a wide modulation range, superior harmonic performance.                |

## 4.2. Real world applications assesment

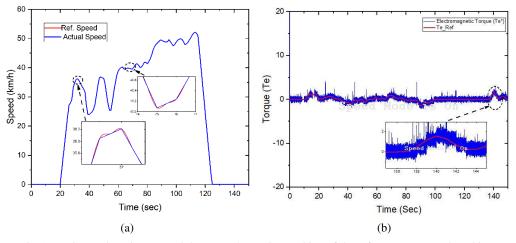

To assess the real-world applicability of the proposed inverter system for EVs, an urban drive cycle was employed to evaluate its performance. Figure 17 illustrates the drive cycle trajectory and the system's precise tracking of the reference, demonstrating the inverter's ability to respond dynamically to the fluctuating demands of an urban driving environment. This result underscores the system's suitability for real-world EV applications, validating its capacity for accurate speed and torque tracking, as required for efficient and reliable EV operation.

Fig. 17. Drive cycle trajectory and the system's precise tracking of the reference: (a) speed tracking; (b) torque tracking

## 5. Conclusion

In this research, the NLC technique was implemented in a three-phase TCHB multilevel inverter to minimize harmonic distortion. The TCHB inverter requires fewer components than traditional MLI topologies to achieve the same output levels, making it a cost-effective and efficient solution. The NLC technique is straightforward to implement, as it does not require complex calculations like SHE or NVC. Operating at fundamental switching frequency, it reduces switching losses while effectively lowering THD. Unlike other methods that target specific harmonics, NLC optimizes overall harmonic performance. The simulation model was developed using MATLAB/Simulink, and experimental validation was conducted via dSPACE under different load conditions. For the 13-level TCHB inverter with equal DC supply values at a modulation index of 1, the voltage THD was 5.22% (resistive load) and 5.17% (inductive-resistive load) in simulations, further reduced to 4.5% and 4.2% in experiments. These results demonstrate strong agreement between simulation and experimental findings, confirming the effectiveness of the proposed approach. Additionally, a comparative analysis with existing TCHB modulation techniques based on harmonic distortion showed that NLC outperforms traditional methods in THD reduction, particularly at higher voltage levels. This highlights NLC's potential for high-performance applications such as motor drives and grid-connected renewable energy systems.

#### Acknowledgements

This research was funded by the Center of Research and Innovation Management (CRiM) and Faculty of Electrical Technology and Engineering, Universiti Teknikal Malaysia Melaka.

#### References

- [1] Hasan M., Abu-Siada A., Dahidah M.S.A., *A three-phase symmetrical DC-Link multilevel inverter with reduced number of DC Sources*, IEEE Transactions on Power Electronics, vol. 33, no. 10, pp. 8331–8340 (2018), DOI: 10.1109/TPEL.2017.2780849.

- [2] Amani M., Azari M.N., Rezanejad M., Single source self-balanced switched-capacitor multilevel inverter with reduced number of semiconductors, IET Power Electronics, vol. 16, no. 4, pp. 575–583 (2023), DOI: 10.1049/PEL2.12409.

- [3] Chen M., Yang Y., Liu X., Loh P.C., Blaabjerg F., Single-source cascaded multilevel inverter with voltage-boost submodule and continuous input current for photovoltaic applications, IEEE Transactions on Power Electronics, vol. 37, no. 1, pp. 955–970 (2022), DOI: 10.1109/TPEL.2021.3098015.

- [4] Vijeh M., Rezanejad M., Samadaei E., Bertilsson K., *A General Review of Multilevel Inverters Based on Main Submodules: Structural Point of View*, IEEE Transactions on Power Electronics, vol. 34, no. 10, pp. 9479–9502 (2019), DOI: 10.1109/TPEL.2018.2890649.

- [5] Hossain M.S., Mohd Said N.A., Halim W.A., Hossain M.H., *Comparing performance and complexity of TCHB and CHB multilevel inverters using NLC technique*, International Journal of Power Electronics and Drive Systems, vol. 15, no. 1, pp. 292–302 (2024), DOI: 10.11591/ijpeds.v15.i1.pp292-302.

- [6] Rodriguez J., Lai J.-S., Peng F.Z., Multilevel inverters: a survey of topologies, controls, and applications, IEEE Transactions on Industrial Electronics, vol. 49, no. 4, pp. 724–738 (2002), DOI: 10.1109/TIE.2002.801052.

- [7] Hossain M.S., Hasan M.A., Mohd Said N.A., Halim W.A., Jidin A., Reduced Device Count Multilevel Inverter Topology for Renewable Energy Applications: A Brief Review, in 2023 IEEE Conference on Energy Conversion (CENCON) pp. 41–46 (2023), DOI: 10.1109/CENCON58932.2023.10369138.

- [8] Kouro S. et al., Recent Advances and Industrial Applications of Multilevel Converters, IEEE Transactions on Industrial Electronics, vol. 57, no. 8, pp. 2553–2580 (2010), DOI: 10.1109/TIE.2010.2049719.

- [9] Choudhury S., Bajaj M., Dash T., Kamel S., Jurado F., *Multilevel Inverter: A Survey on Classical and Advanced Topologies, Control Schemes, Applications to Power System and Future Prospects*, Energies, vol. 14, no. 18, 5773 (2021), DOI: 10.3390/EN14185773.

- [10] Mahato B., Ranjan M., Pal P.K., Gupta S.K., Mahto K.K., Design, development and verification of a new multilevel inverter for reduced power switches, Archives of Electrical Engineering, vol. 71, no. 4, pp. 1051–1063 (2022), DOI: 10.24425/aee.2022.142124.

- [11] Anisetty S.K., Sri Gowri K., Rao S.N., Kiran P.S., Kumar K.N., *Integer factor based SVPWM approach for multilevel inverters with continuous and discontinuous switching sequences*, Archives of Electrical Engineering, vol. 70, no. 4, pp. 859–872 (2021), DOI: 10.24425/aee.2021.138266.

- [12] Mechouma R., Azoui B., Chaabane M., *Three-phase grid connected inverter for photovoltaic systems, a review*, in 2012 First International Conference on Renewable Energies and Vehicular Technology, pp. 37–42 (2012), DOI: 10.1109/REVET.2012.6195245.

- [13] Swamy D.M., Venkatesan M., Three Phase Multi-Level Inverter Topologies and Modulation Techniques: A Short review, in 2019 2nd International Conference on Intelligent Computing, Instrumentation and Control Technologies (ICICICT), vol. 1, pp. 305–311 (2019), DOI: 10.1109/ICICICT46008.2019.8993140.

- [14] Rodriguez J., Bernet S., Wu B., Pontt J.O., Kouro S., Multilevel Voltage-Source-Converter Topologies for Industrial Medium-Voltage Drives, IEEE Transactions on Industrial Electronics, vol. 54, no. 6, pp. 2930–2945 (2007), DOI: 10.1109/TIE.2007.907044.

- [15] Maheswari K.T., Bharanikumar R., Arjun V., Amrish R., Bhuvanesh M., *A comprehensive review on cascaded H-bridge multilevel inverter for medium voltage high power applications*, Materials Today: Proceedings, vol. 45, pp. 2666–2670 (2021), DOI: 10.1016/j.matpr.2020.11.519.

- [16] Bidin J., Iskandar M., Yusof I., Ab Rahman M.Z., Azri M., *Performance Evaluation of Single Phase Transformerless Inverter for Grid-connected Photovoltaic Application*, International Journal of Electrical Engineering and Applied Sciences, vol. 4, no. 2, pp. 9–18 (2021), accessed: 2023 [online], available: https://ijeeas.utem.edu.my/ijeeas/article/view/6065.

- [17] Chen H., Zhao H., Review on pulse-width modulation strategies for common-mode voltage reduction in three-phase voltage-source inverters, IET Power Electronics, vol. 9, no. 14, pp. 2611–2620 (2016), DOI: 10.1049/iet-pel.2015.1019.

- [18] Ali M., Al-Ismail F.S., Gulzar M.M., Khalid M., *A review on harmonic elimination and mitigation techniques in power converter based systems*, Electric Power Systems Research, vol. 234, 110573 (2024), DOI: 10.1016/j.epsr.2024.110573.

- [19] El Maataoui W., El Daoudi S., Abounada A., Mabrouki M., A comparative study of virtual synchronous generator and sinusoidal pulse width modulation in a wind high power conversion chain, Archives of Electrical Engineering, vol. 73, no. 4, pp. 961–976 (2024), DOI: 10.24425/aee.2024.152105.

- [20] Zolfagharian O., Dastfan A., Marzebali M.H., Selective Harmonic Elimination Technique Improvement for Cascaded H-Bridge Multilevel Converters Under DC Sources Uncertainty, IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 12, no. 2, pp. 1282–1293 (2024), DOI: 10.1109/JESTPE.2023.3271653.

- [21] Rao S.N., Kumar D.V.A., Babu C.S., *New multilevel inverter topology with reduced number of switches using advanced modulation strategies*, in 2013 International Conference on Power, Energy and Control (ICPEC), pp. 693–699 (2013), DOI: 10.1109/ICPEC.2013.6527745.

- [22] Sinha A., Jana K.C., Das M.K., An inclusive review on different multi-level inverter topologies, their modulation and control strategies for a grid connected photo-voltaic system, Solar Energy, vol. 170, pp. 633–657 (2018), DOI: 10.1016/j.solener.2018.06.001.

- [23] Blaabjerg F., Chen Z., Kjaer S.B., *Power electronics as efficient interface in dispersed power generation systems*, IEEE Transactions on Power Electronics, vol. 19, no. 5, pp. 1184–1194 (2004), DOI: 10.1109/TPEL.2004.833453.

- [24] Buccella C., Cecati C., Cimoroni M.G., Razi K., Harmonic mitigation technique for multilevel inverters in power systems, in 2014 International Symposium on Power Electronics, Electrical Drives, Automation and Motion, pp. 73–77 (2014), DOI: 10.1109/SPEEDAM.2014.6872070.

- [25] Jayal P., Bajpai G., A novel space vector modulation-based transistor-clamped H bridge inverter-fed permanent magnet synchronous motor drive for electric vehicle applications, IET Power Electronics, vol. 31, no. 3 (2021), DOI: 10.1002/2050-7038.12789.

- [26] Khergade A.V., Satputaley R.J., Borghate V.B., Raghava B.V.S., Harmonics Reduction of Adjustable Speed Drive Using Transistor Clamped H-Bridge Inverter Based DVR With Enhanced Capacitor Voltage Balancing, IEEE Transactions on Industrial Applications, vol. 56, no. 6, pp. 6744–6755 (2020), DOI: 10.1109/TIA.2020.3013823.

- [27] Belkacem R.E.M., Benzid R., Bouguechal N., *Multilevel inverter with optimal THD through the firefly algorithm*, Archives of Electrical Engineering, vol. 66, no. 1, pp. 73–81 (2017), DOI: 10.1515/aee-2017-0010.

- [28] Singh P., Tiwari S., Gupta K.K., *A new topology of transistor clamped 5-level H-Bridge multilevel inverter with voltage boosting capacity*, in PEDES 2012 IEEE International Conference on Power Electronics, Drives and Energy Systems, pp. 1–5 (2012), DOI: 10.1109/PEDES.2012.6484381.

- [29] Goswami S.K., *Harmonics elimination in a multilevel inverter using the particle swarm optimisation technique*, IET Power Electronics, vol. 2, no. 6, pp. 646–652 (2009) [online], available: https://digitallibrary.theiet.org/content/journals/10.1049/iet-pel.2008.0180.

- [30] Bin Arif M.S. et al., An improved asymmetrical multi-level inverter topology with boosted output voltage and reduced components count, IET Power Electronics, vol. 14, no. 12, pp. 2052–2066 (2021), DOI: 10.1049/pel2.12119.

- [31] Hossain M.S., Hossain M.I., Mohd Said N.A., Halim W.A., Azam S.N.M., Hossain M.H., Nearest Level Control Technique for Three-phase Transistor Clamped H-bridge Multilevel Inverter, in 2022 IEEE International Conference on Power and Energy, pp. 71–76 (2022), DOI: 10.1109/PECON54459.2022.9988919.

- [32] Perez M., Rodriguez J., Pontt J., Kouro S., *Power Distribution in Hybrid Multi-cell Converter with Nearest Level Modulation*, in 2007 IEEE International Symposium on Industrial Electronics, pp. 736–741 (2007), DOI: 10.1109/ISIE.2007.4374688.

- [33] José R., Agelidis V., Multilevel converters: An enabling technology for high-power applications, Proceedings of the IEEE, vol. 97, no. 11, pp. 1786–1817 (2009), DOI: 10.1109/JPROC.2009.2030235.

- [34] Halim W.A., Rahim N.A., Azri M., Selective harmonic elimination for a single-phase 13-level TCHB based cascaded multilevel inverter using FPGA, Journal of Power Electronics, vol. 14, no. 3, pp. 488–498 (2014), DOI: 10.6113/JPE.2014.14.3.488.

- [35] Deng Y., Harley R.G., Space-Vector Versus Nearest-Level Pulse Width Modulation for Multi-level Converters, IEEE Trans. Power Electron., vol. 30, no. 6, pp. 2962–2974 (2015), DOI: 10.1109/TPEL.2014.2331687.

- [36] Sarwar M., Sarwar A., Farooqui S., Moht. T.-I., Mohhamad Fahad, Abdul R. Beig, A Hybrid Nearest Level Combined with PWM Control Strategy: Analysis and Implementation on Cascaded H-Bridge Multilevel Inverter and its Fault Tolerant Topology, ieeexplore.ieee.org., accessed: 2023 [online], available: https://ieeexplore.ieee.org/abstract/document/9350652/.

- [37] Halim W.A., Rahim N.A., Azri M., Selective harmonic elimination for a single-phase 13-level TCHB based cascaded multilevel inverter using FPGA, J. Power Electron., vol. 14, no. 3, pp. 488–498 (2014), DOI: 10.6113/JPE.2014.14.3.488.

- [38] Sai Lalitha A., Reddy R., *Performance evaluation of transistor clamped h-bridge (TCHB) based five-level multilevel inverter topologies*, Lect. Notes Electr. Eng., vol. 5, no. 3, pp. 102–125 (2018) [online], available: https://ijrar.org/papers/IJRAR1903262.pdf.

- [39] Rameshkumar K., Indragandhi V., Mani G., Sanjeevikumar P., Model predictive current control of single-phase 13-level transistor-clamped H-bridge based cascaded multilevel inverter, Lect. Notes Electr. Eng., vol. 436, pp. 597–608 (2017), DOI: 10.1007/978-981-10-4394-9\_58.

- [40] Rasheed M., Alakkad M.M.A., Omar R., Sulaiman M., Halim W.A., *Enhance the accuracy of control algorithm for multilevel inverter based on artificial neural network*, Indones. J. Electr. Eng. Comput. Sci., vol. 20, no. 3, pp. 1148–1158 (2020), DOI: 10.11591/ijeecs.v20.i3.pp1148-1158.

- [41] Meshram P.M., Borghate V.B., *A simplified nearest level control (NLC) voltage balancing method for modular multilevel converter (MMC)*, IEEE Trans. Power Electron., vol. 30, no. 1, pp. 450–462 (2015), DOI: 10.1109/TPEL.2014.2317705.

- [42] Hossain M.S., Said N.A.M., Hasan M.A., Halim W.A., Munim W.N.W.A., Jidin A., *Performance evaluation of a nearest level control-based TCHB multilevel inverter for PMSM motors in electric vehicle systems*, Results Eng., vol. 25, 103949 (2025), DOI: 10.1016/j.rineng.2025.103949.