INTL JOURNAL OF ELECTRONICS AND TELECOMMUNICATIONS, Manuscript received December 31, 2011; revised March 2012.

let

# Synthesis of FSMs Based on Architectural Decomposition with Joined Multiple Encoding

VOL

DOI: 10.2478/v10177-012-0005-7

Arkadiusz Bukowiec

Abstract—The method of synthesis of the logic circuit of finite state machine (FSM) with Mealy's outputs is proposed in this paper. Proposed method is based on the innovate encoding of microinstructions split into subsets. Code of microinstruction is represented as a part of current state code and code of microinstruction inside of current subset. It leads to realization of FSM as s double-level structure. It leads to diminishing of number of variables required for encoding of microinstructions. Such approach permits to decrease the number of required outputs of combinational part of FSM.

Keywords-Boolean algebra, circuit synthesis, Field Programmable Gate Arrays, sequential circuits.

### I. INTRODUCTION

**F** INITE state machines (FSMs) with Mealy's outputs [1], [2] are one of the most popular method of control units (CUs) design. Nowadays, field programmable gate arrays (FPGAs) are used very often for implementation of logic circuits of FSMs [3], [4]. One of the main features of FPGA is existence of logic elements with restricted number of inputs [5]. On the other hand, logic functions of FSMs have much more arguments than number of inputs of typical logic element. This imbalance leads to necessity of decomposition of logic functions describing the behavior of FSM [6], [7], [8]. The negative results of functional decomposition are both increasing a number of levels of the FSM circuit and decreasing of a digital system performance in comparison to single-level implementation of control unit.

One of methods of decreasing a number of logic functions depending on big number of arguments is multi-level implementation of FSM [9], [10]. Such methods required additional internal variables and very often consume more hardware then single-level implementation of FSM. But, this issue can be resolved by usage of both, logic elements and embedded memory blocks, that are available in modern FPGA devices.

The method of decreasing of a number of functions depending of logic conditions and internal variables of FSM is proposed in given article. There is proposed method of joined multiple encoding of microinstructions. A set of microinstruction is divided into subsets based on a current state [11]. Then, subset are joined into pairs [12]. Each pair is identified based on a part of state code [13]. Next, microinstruction are encoded separately in each pair of subsets. The microinstruction encoding leads to decrease the number of implemented logic functions by combinational part of the logic circuit. And the

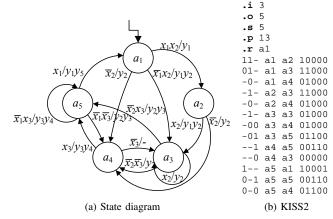

Fig. 1. Example of FSM S<sub>1</sub>.

www.journals.pan.pl 58, NO. 1, PP. 35–41

joining of subsets leads to decrease size of memory decoder. In overall it leads to balanced usage of different kind of logic resources.

#### **II. RUDIMENTS**

A finite state machine is a mathematical model of behavior composed of a finite set of input symbols, a finite set of states, a finite set of output symbols, transitions and actions. It is represented as 6-tuple:

$$S = \langle X, Y, A, a_1, \delta, \omega \rangle,$$

where: X

a

is a finite set of input symbols,  $X = \{x_1, \ldots, x_L\}$ ;

Yis a finite set of output symbols,  $Y = \{y_1, \ldots, y_N\};$ is a finite non empty set of states, A =Α

$\{a_1,\ldots,a_M\};$

is the initial state,

$$a_1 \in A$$

;

δ is a transition function, defined as a function of a state and input symbols:

$$\delta: A \times X \to A; \tag{2}$$

(1)

is an output function, in case of Moore model [14] ω defined as a function of a state:

$$\omega: A \to Y,\tag{3}$$

and in case of Mealy model [15] defined as a function of a state and input symbols:

$$\omega: A \times X \to Y. \tag{4}$$

One of the most popular methods of representation of FSMs is KISS2 text format [16]. It is a text file (Fig. 1b)

This work was supported by the Ministry of Science and Higher Education of Poland. Research grant no. N516 513939 for years 2010-2013.

A. Bukowiec is with the Institute of Computer Engineering and Electronics, University of Zielona Góra, Licealna 9, 65-417 Zielona Góra, Poland (e-mail: a.bukowiec@iie.uz.zgora.pl).

36

www.czasopisma.pan.pl

representation of one-dimensional state transition table [1], [2]. A file in this format consists of two parts: header and table. The header includes information about the number of inputs .i, the number of outputs .o, the number of table products .p, the number of states .s, and the initial state (optional) .r. The table describes the behavior (transitions) of a FSM. It consists of four columns: a logic condition, a current state, a next state, and output variables. The '-' sign in logic condition means that this input variable does not affect this transition. The '0' value means that negation of this variable should be placed in a logic condition and the '1' value that its affirmation should be placed in a logic condition.

## **III. SYNTHESIS METHODS**

Logic circuit of Mealy FSM can be described as system of logic functions:

$$\Phi = \Phi(X, Q),$$

$$Y = Y(X, Q),$$

(5)

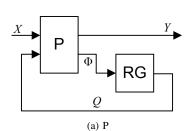

where  $Q = \{Q_1, \ldots, Q_R\}$  is a set of internal variables, that are used to encode states of FSM  $a_m \in A$ , and  $R = \log_2 M$ ;  $\Phi = \{D_1, \ldots, D_R\}$  is a set of excitation functions. This system is formed based on transition table (e.g. described in KISS2 file) during logic synthesis process. It is also the basis to form single-level logic circuit of FSM, called P (Fig. 2a) [1], [2]. Here the combinational circuit P implements system of excitation functions and microoperations (5) and it is implemented with use of logic elements in FPGAs. The register RG implements the memory of FSM and it has D type inputs as a rule.

In this structure, the total number of logic functions implemented by combinational circuit P is equal to:

$$n_{\rm P}({\rm P}) = R + N. \tag{6}$$

One of the known methods of reduction of this value is application of the maximal encoding of microinstructions [2]. Let transition table has T different microinstructions  $Y_t \subseteq Y$ . Let encode each microinstruction  $Y_t$  by binary code  $K(Y_t)$ with  $N_1 = \lceil \log_2 T \rceil$  bits, where  $N_1 < N$ . Let use variables  $z_n \in Z = \{z_1, \ldots, z_{N_1}\}$  for representation of these codes. In this case, the logic circuit of FSM can be implemented with a double-level structure PY (Fig. 2b) [1], [2]. Here, the combinational circuit P implements system of excitation functions and microinstructions encoding:

$$\Phi = \Phi(X, Q),$$

$$Z = Z(X, Q),$$

(7)

but the number of implemented logic functions is reduced to:

$$n_{\rm PY}(\mathbf{P}) = R + N_1. \tag{8}$$

The register RG has exactly the same function like in a previous structure. The additional circuit Y implements system of microinstruction decoder:

$$Y = Y(Z),\tag{9}$$

and, because of its regular structure, it can be implemented with use of embedded blocks in FPGAs. However, the value of (8) is still relatively big in comparison to (6) and it does not assure reduction of the number of required logic elements to implementation of combinational circuit P [17]. It makes that application of this structure in FPGAs not effective.

Further reduction of the number of implemented logic functions can be satisfied by application of multiple encoding of microinstructions [10], [13]. Let divide set of microinstructions  $\Upsilon = \{Y_1, \ldots, Y_T\}$  into subsets based on current state  $a_m$ . It leads to existence of M subsets  $\Upsilon(a_m) \subseteq \Upsilon$ ,  $\Upsilon = \{\Upsilon(a_1), \ldots, \Upsilon(a_M)\}$  and microinstruction  $Y_t \in \Upsilon(a_m)$ iff it is executed during any transition from state  $a_m$ . Let encode each microinstruction  $Y_t \in \Upsilon(a_m)$  by binary code  $K_m(Y_t)$  with  $N_0 = \lceil \log_2 T_0 \rceil$  bits where:

$$T_0 = \max(|\Upsilon(a_1)|, \dots, |\Upsilon(a_M)|).$$

(10)

Let use variables  $\psi_n \in \Psi = {\psi_1, \ldots, \psi_{N_0}}$  for representation of these codes. In this case code of microinstruction  $K(Y_t)$ is represented by concatenation of multiple code of microinstruction  $K_m(Y_t)$  and code of current state  $K(a_m)$ :

$$K(Y_t) = K_m(Y_t) * K(a_m).$$

(11)

Digital circuit of FSM with such encoding can be implemented with a double-level structure  $PY_0$  (Fig. 2c) [17], [11]. Now, the combinational circuit P implements system of excitation functions and microinstructions multiple encoding:

$$\Phi = \Phi(X, Q),$$

$$\Psi = \Psi(X, Q),$$

(12)

and the number of implemented logic functions is equal to:

$$n_{\rm PY_0}({\rm P}) = R + N_0.$$

(13)

The register RG has exactly the same function like in previous structures. There is also additional circuit Y. It implements system of microinstruction multiple decoder:

$$Y = Y(\Psi, Q), \tag{14}$$

and it also can be implemented with use of embedded blocks in FPGAs. In this case, the value of (13) gives possibility to reduce the number of required logic elements for implementation of combinational circuit P [17]. Unfortunately, implementation of the microinstruction multiple decoder Y, represented by system (14), can lead to not effective usage of embedded memory block of FPGAs.

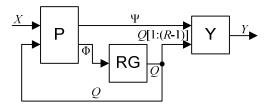

## IV. Synthesis Methods with Joined Multiple Encoding

The idea of presented in this article method of synthesis is based on joining of microinstructions subsets into pair. It leads to possibility of identification of microinstruction only with use of a part of a current state code. This solution causes that the microinstruction decoder memory size is decreased twice and there is no need to implement any additional logic functions by combinational circuit.

Let join subsets  $\Upsilon(a_m)$  into pairs  $\Upsilon_{m'}^{m''} = \Upsilon(a_{m'}) \cup \Upsilon(a_{m''})^1$  and all such pair create a set  $\Upsilon^{\mathbf{P}}$ . The number of elements of all pairs  $\Upsilon_{m'}^{m''}$  should be equalized. Iff  $M < 2^{\lceil \log_2 M \rceil}$

<sup>&</sup>lt;sup>1</sup>Each pair is represented as a sum of two subsets.

synthesis of FSMS Based on Architectural Decomposition with Joined Multiple Encoding

Ρ

RG

(b) PY

Fig. 2. Structures of logic circuit of FSM.

Fig. 3. Structure of logic circuit of  $PY_J$  FSM.

then  $2^{\lceil \log_2 M \rceil} - M$  the biggest subsets  $\Upsilon(a_m)$  should be joined into pair with empty set  $\varnothing$  ( $\Upsilon_{m'}^{\varnothing} = \Upsilon(a_{m'}) \cup \varnothing$ )). The remain subsets are joined into pair by the rule: The biggest with the smallest. Next, let encode states  $a_{m'}$  and  $a_{m''}$  of each pair by binary codes  $K(a_{m'})$  and  $L(a_{m''})$  with R bits. These codes should differ only on the least significant bit  $Q_R$ . Now, let encode microinstruction for each pair of subsets by binary code  $K_{m'}^{m''}(Y_t)$  on  $N_C = \lceil \log_2 T_C \rceil$  bits, where

$$T_C = \max_{m'=1,m''=1}^{M,M} (|\Upsilon_{m'}^{(m'')}|).$$

(15)

Application of this is effective only if condition:

$$N_C = N_0 \tag{16}$$

is satisfied. Otherwise, the number of logic function implemented by combinational circuit is increased and length of multiple code of microinstruction is also increased. It causes also that memory size is not reduced. But, for typical control algorithms condition (16) should be satisfied.

Let us use variables  $\psi_n \in \Psi = \{\psi_1, \ldots, \psi_{N_C}\}$  for representation of the code  $K_{m'}^{m''}(Y_t)$ . When such encoding is applied, there is required to use concatenation of multiple code of microinstruction  $K_{m'}^{m''}(Y_t)$  and part of the code of current state  $K(a_m)[1:(R-1)]$ :

$$K(Y_t) = K_{m'}^{m''}(Y_t) * K(a_m)[1:(R-1)].$$

(17)

for one to one representation of the code of microinstruction  $K(Y_t)$ .

For this encoding, the logic circuit of FSM can be implemented with a double-level structure  $PY_J$  (Fig. 3). Here, the combinational circuit P implements system of excitation functions and microinstructions joined multiple encoding:

$$\Phi = \Phi(X, Q),$$

$$\Psi = \Psi(X, Q),$$

(18)

Q (c) PY<sub>0</sub> 1:  $T_0 = 0$ 2:  $\Upsilon = \varnothing$ for m = 1 to M do 3:  $\Upsilon(\text{States}[m]) = \emptyset$ 4: 5: for h = 1 to H do if AM(h) = = States[m] then 6: 7:  $\Upsilon(a_m) \rightarrow \operatorname{ADD}(\operatorname{YH}(h))$ end if 8: 9: end for 10:  $\Upsilon \rightarrow ADD(\Upsilon(States[m]))$ if  $(\Upsilon(\text{States}[m]) \rightarrow \text{COUNT} > T_0)$  then 11:  $T_0 = \Upsilon(\text{States}[m]) \rightarrow \text{Count}$ 12: 13: end if

Ρ

Φ

Ψ

RG

Fig. 4. Algorithm of creation and division of microinstructions.

and the number of implemented logic functions is equal to:

$$n_{\mathrm{PY}_{\mathrm{I}}}(\mathrm{P}) = R + N_C. \tag{19}$$

Because of (16) this value is unchanged in comparison to previous method. And it still can be implemented using logic blocks of FPGA without big impact on the logic blocks number. The register RG has exactly the same function like in previous structures. There is also circuit Y. It implements system of microinstruction joined multiple decoder:

$$Y = Y(\Psi, Q[1:R-1]),$$

(20)

and it also can be implemented with use of embedded blocks in FPGAs. Because the address word is shorter by one bit in comparison to  $PY_0$  structure the size of memory is decreased twice.

The whole synthesis process includes following steps:

- Creation and division of microinstructions set. Let us create set of microinstructions Υ = {Y<sub>1</sub>,...,Y<sub>T</sub>} by readout all unique microinstructions Y<sub>t</sub> from transition table. Then, this set is divided into M subsets based on current state A<sub>m</sub>. Each subset Υ(a<sub>m</sub>) ⊆ Υ consists only of microinstructions that are executed during any transition from state a<sub>m</sub>. Implemented algorithm (Fig. 4) is optimized and creates divided subsets directly from transition table.

- 2. Joining of microinstruction subsets into pairs. Let us join all subsets  $\Upsilon(a_m)$  into pair  $\Upsilon_{m'}^{m''}$  by applying rule described above and i9mplemented in algorithm shown in Figure 5.

38

1:  $\Upsilon \rightarrow Sort$ 2:  $\Upsilon^{\mathbf{P}} = \emptyset$ 3:  $M_P = 2^{\lceil \log_2 M \rceil} - M$ 4: **if**  $M_P > 0$  **then** for m = 1 to  $M_P$  do 5:  $\Upsilon^P(m) = \emptyset$ 6:  $\Upsilon^P(m) \to a_{m'} = \Upsilon[m] \to a_m$ 7:  $\Upsilon^P(m) \rightarrow \text{ADDELEM}(\Upsilon[m])$ 8:

$$\begin{split} \Upsilon^{P}(m) &\to a_{m''} = \Upsilon[m] \to \varnothing \\ \Upsilon^{\mathbf{P}} &\to \mathrm{ADD}(\Upsilon^{P}(m)) \end{split}$$

9: 10: end for 11: end if 12: for  $m = M_P + 1$  to  $\frac{M - M_P}{2}$  do 13:  $\Upsilon^P(m) = \emptyset$ 14:  $\Upsilon^P(m) \to a_{m'} = \Upsilon[m] \to a_m$ 15:  $\Upsilon^P(m) \rightarrow \text{ADDELEM}(\Upsilon[m])$ 16:  $\Upsilon^P(m) \to a_{m''} = \Upsilon[m] \to a_m$ 17:  $\Upsilon^P(m) \rightarrow \text{ADDELEM}(\Upsilon[M - (m - (M_P + 1))])$ 18:  $\Upsilon^{\mathbf{P}} \to \operatorname{ADD}(\Upsilon^{P}(m))$ 19 20: end for

www.czasopisma.pan.pl

Fig. 5. Algorithm of joining of microinstructions.

- 3. Encoding of microinstructions. Let us encode each microinstruction  $Y_t$  in each pair  $\Upsilon_{m'}^{m''}$  by binary code  $K_{m'}^{m''}(Y_t)$ (Fig. 6).

- 4. Encoding of states. There is required a special encoding of states to satisfy the possibility of encoding of microinstruction with usage of partial code of current state. So, let us encode states  $a_{m'}$  and  $a_{m''}$  defining each pair  $\Upsilon_{m'}^{m''}$ by following binary codes  $K(a_{m'})$  and  $K(a_{m''})$ . It assures that these codes differ only on least significant bit  $Q_R$ . The algorithm presented in Figure 7 overwrites existing trivial binary encoding that is used by other synthesis methods by new codes.

- 5. Formation of direct structural table of  $FSM PY_J$ . This table is formatted based on original transition table by adding columns with: code of current state  $K(a_m)$ , code of next state  $K(a_s)$ , excitation functions  $\Phi_h$  that are equal to 1 to switch the FSM memory form code  $K(a_m)$  to  $K(a_s)$ , and by replacing microinstruction column  $Y_h$  by column  $\Psi_h$ . The column  $\Psi_h$  consists variables that are equal to 1 in adequate code  $K_{m'}^{m''}(Y_t)$ . This table is a basis for formation of the system (18). The application for synthesis omits this step because all data for this table is created in previous steps and the table is required only for presentation purpose and manual synthesis. The application store the FSM model in table that are red from KISS2 file and additional collections.

- 6. Formation of table of microinstruction decoder. This table has columns:  $K_{m'}^{m''}(Y_t)$ ,  $K(a_m)[1:(R-1)]$ ,  $K(Y_t)$ . This table is basis for formation of the system (20). From similar reason like in previous step this table is also not created by the application for synthesis. The application creates the description of Y circuit in Verilog HDL in this step.

- 7. Formation of logic equations. This step is required to form Boolean equations describing the system (18). They are created based on direct structural table of FSM PY<sub>J</sub> as

1:  $\mathbf{K}(\mathbf{\Upsilon}^{\mathbf{P}}) = \emptyset$ 2: for m = 1 to  $|\Upsilon^{\mathbf{P}}|$  do  $K(\Upsilon^P(m)) = \varnothing$ for t = 1 to  $|\Upsilon^{\mathbf{P}}[m]|$  do  $K(\Upsilon^{P}(m)) \rightarrow \text{Add}(\text{IntToBin}(t, N_{C}))$

5:

$\mathbf{K}(\Upsilon^{\mathbf{P}}) \rightarrow \mathrm{ADD}(K(\Upsilon^{P}(m)))$ 7:

8: end for

3:

4:

Fig. 6. Algorithm of encoding of microinstructions.

1: for m = 1 to  $|\Upsilon^{\mathbf{P}}|$  do 2:  $K(A)[\Upsilon^{\mathbf{P}}[m] \rightarrow a_{m'} \rightarrow m] = \text{IntToBin}((m-1) *$ 2,R) if  $\Upsilon^{\mathbf{P}}[m] \to a_{m''} \neq \emptyset$  then  $K(A)[\Upsilon^{\mathbf{P}}[m] \to a_{m''} \to m] = \text{IntToBin}((m *$ 3: 4: 2 - 1, R) end if 5: 6: end for

Fig. 7. Algorithm of encoding of states.

sum of products in typical way [1], [2]. The application for synthesis builds equations in Verilog HDL. These equations create description of P circuit.

8. Implementation of logic circuit into FPGA. The combinational circuit P and the register RG are implemented with use of standard logic blocks. The circuit P with use of look-up tables and the register RG with D type flipflops. The decoder Y is implemented with use of embedded memory blocks. The address is represented by (17) and microinstructions from sets  $\Upsilon_{m'}^{m''}$  creates content of this memory.

To satisfy such implementation, the whole circuit could be described with use of HDLs in approbate way, and then it should be passed into third party synthesis & implementation tools. The logic equations of the system (18) of combinational circuit P should be described with use of continuous assignment. The register RG should be described as *R*-bits D type flip-flop with use of standard synthesis template [18], [19]. The circuit Y has to be described as process with clock signal on the sensitivity list. It should be trigged by opposite edge of clock signal than the register RG. It satisfies that outputs are stable after one clock cycle [17]. The reset signal should be described as synchronous one and the content of the memory could be described with use of case statement with address as a selector. Additionally, there have to be added special synthesis directive to permit implementation with use of embedded memory blocks. The syntax of this directive depends on selected FPGA vendor. The top-level module could be described as connection of instantiated components.

## V. METHOD APPLICATION ON EXAMPLE

The synthesis process described in previous section will be illustrated on example FSM  $S_1$  (Fig. 1) [17]. There is M = 5states in this FSM and they create the set  $A = \{a_1, \ldots, a_5\}$ .

A. BUKOWIEC

There is also N = 5 microoperations  $Y = \{y_1, \ldots, y_5\}$ . These microoperations create T = 7 microinstructions

$$\Upsilon = \left\{ \begin{array}{l} Y_1 = \{y_1\}, Y_2 = \{y_1, y_2\}, Y_3 = \{y_2\}, \\ Y_4 = \{y_2, y_3\}, Y_5 = \{y_3, y_4\}, \\ Y_6 = \emptyset, Y_7 = \{y_1, y_5\} \end{array} \right\}$$

There is required to use  $N_1 = \lceil \log_2 T \rceil = 3$  bits to encode all microinstructions in case of application of PY structure (Fig. 2b). It means, that the combinational circuit P have to implement  $n_{PY}(P) = R + N_1 = 6$  logic functions and the decoder Y can be implemented as a memory block with 3-bit address and 5-bit word.

The application of PY<sub>0</sub> structure (Fig. 2c) is also possible. In this case, there is required to use  $N_0 = \lceil \log_2 T_0 \rceil = 2$  bits to encode microinstructions. And now, that the combinational circuit P has to implement  $n_{PY_0}(P) = R + N_0 = 5$  Boolean functions and the decoder Y can be implemented with use of a memory block with 5-bit address and and 5-bit word. It can be noticed that there is required to store more words in the memory but size of memory block does not change because the number of available block is not exceeded. Of course in other cases it can be exceeded and then the application of proposed method with joined encoding can be helpful.

The synthesis with joined multiple encoding of microinstructions into PY<sub>J</sub> structure (Fig. 3) starts with division of microinstructions set into subsets based on current state (step 1). In our example, there is M = 5 such subsets:  $\Upsilon(a_1) = \{Y_1, Y_2, Y_3\}, \ \Upsilon(a_2) = \{Y_2, Y_3\}, \ \Upsilon(a_3) = \{Y_3, Y_4\},\$  $\Upsilon(a_4) = \{Y_5, Y_6\}$ , and  $\Upsilon(a_5) = \{Y_4, Y_5, Y_7\}$ . Next, there is required to join these subsets into pairs (step 2). This is the most important step of this synthesis method. Because, for the example FSM S<sub>1</sub>, the condition  $M < 2^{\lceil \log_2 M \rceil}$  is satisfied the three biggest subsets are joined with empty set  $\emptyset$  into pair. So, there are created four pairs:  $\Upsilon_1^{\varnothing} = \{Y_1, Y_2, Y_3\}, \ \Upsilon_5^{\varnothing} = \{Y_4, Y_5, Y_7\}, \ \Upsilon_2^{\varnothing} = \{Y_1, Y_2\}, \ \text{and} \ \Upsilon_3^{4} = \{Y_3, Y_4, Y_5, Y_6\}.$ Now, the microinstruction can be encoded with binary code  $K_{m'}^{m''}(Y_t)$  (step 3). In our case there is required to use

$$\begin{split} &N_{C} = \lceil \log_{2} T_{C} \rceil = 2 \text{ bits to represent this code and encoding} \\ &N_{C} = \lceil \log_{2} T_{C} \rceil = 2 \text{ bits to represent this code and encoding} \\ &\text{looks as follow: } K_{1}^{\varnothing}(Y_{1}) = 00, \ K_{1}^{\varnothing}(Y_{2}) = 01, \ K_{1}^{\varnothing}(Y_{3}) = 10, \\ &K_{5}^{\varnothing}(Y_{4}) = 00, \ K_{5}^{\varnothing}(Y_{5}) = 01, \ K_{5}^{\varnothing}(Y_{7}) = 10, \ K_{2}^{\varnothing}(Y_{1}) = 00, \\ &K_{2}^{\varnothing}(Y_{2}) = 01, \ K_{3}^{4}(Y_{3}) = 00, \ K_{3}^{4}(Y_{4}) = 01, \ K_{3}^{4}(Y_{5}) = 10, \\ &K_{2}^{\varnothing}(Y_{2}) = 01, \ K_{3}^{4}(Y_{3}) = 00, \ K_{3}^{4}(Y_{4}) = 01, \ K_{3}^{4}(Y_{5}) = 10, \end{split}$$

and  $K_3^4(Y_6) = 11$ . To encode microinstructions there is required to use adequate state encoding (step 4). Because codes of states  $K(a_{m'})$  and  $K(a_{m''})$  have to differ on one last least significant bit  $Q_R$  the states could be encoded as follow:  $K(a_1) = 000, K(a_2) = 010, K(a_3) = 100, K(a_1) = 101,$ and  $K(a_5) = 110$  for our example. It can be noticed that codes 001, 111, and 011 can not be assigned to any state because subsets  $\Upsilon(a_{m'})$  depending on states  $a_1, a_5$ , and  $a_2$  are joined with empty set  $\varnothing$ . Now, the transformed direct structural table of FSM PY<sub>J</sub> (step 5.) can be created. It is presented in Table I for example FSM S<sub>1</sub>. There is also required to create table of the decoder Y (step 6). It describes content of the memory. It is presented in Table II for example FSM S<sub>1</sub>. Based on the transformed DST (Tab. I) there can be formed logic equations of system (18) (step 7). For our example FSM  $S_1$ , there can

TABLE I

TRANSFORMED DST OF THE MEALY FSM S1

| $a_m$ | $K(a_m)$ | $a_s$   | $K(a_s)$ | $X_h$                           | $\Psi_h$        | $\Phi_h$  | h  |

|-------|----------|---------|----------|---------------------------------|-----------------|-----------|----|

| $a_1$ | 000      | $a_2$   | 010      | $x_1 x_2$                       |                 | $D_2$     | 1  |

|       |          | $a_3$   | 100      | $\overline{x_1} x_2$            | $\psi_2$        | $D_1$     | 2  |

|       |          | $a_4$   | 101      | $\overline{x_2}$                | $\psi_1$        | $D_1 D_3$ | 3  |

| $a_2$ | 010      | $a_3$   | 100      | $x_2$                           |                 | $D_1$     | 4  |

|       |          | $a_4$   | 101      | $\overline{x_2}$                | $\psi_2$        | $D_1 D_3$ | 5  |

| $a_3$ | 100      | $a_3$   | 100      | $x_2$                           |                 | $D_1$     | 6  |

|       |          | $ a_4 $ | 101      | $\overline{x_2} \overline{x_3}$ |                 | $D_1 D_3$ | 7  |

|       |          | $a_5$   | 110      | $\overline{x_2} x_3$            | $\psi_2$        | $D_1 D_2$ | 8  |

| $a_4$ | 101      | $a_5$   | 110      | $x_3$                           | $\psi_1$        | $D_1 D_2$ | 9  |

|       |          | $a_3$   | 100      | $\overline{x_3}$                | $\psi_1 \psi_2$ | $D_1$     | 10 |

| $a_5$ | 110      | $a_1$   | 000      | $x_1$                           | $\psi_1$        |           | 11 |

|       |          | $a_5$   | 110      | $\overline{x_1} x_3$            | $\psi_2$        | $D_1 D_2$ | 12 |

|       |          | $a_4$   | 101      | $\overline{x_1} \overline{x_3}$ |                 | $D_1 D_3$ | 13 |

TABLE II Table of Decoder Y

| $K(a_m)[1:2]$ | $\begin{array}{c}K_{m'}^{m''}(Y_t)\\\psi_1\psi_2\end{array}$ | $Y_t$                 | $t_0$ |

|---------------|--------------------------------------------------------------|-----------------------|-------|

| $Q_1Q_2$      | $\psi_1\psi_2$                                               | $y_1 y_2 y_3 y_4 y_5$ |       |

| 00            | 00                                                           | 10000                 | 1     |

| 00            | 01                                                           | 11000                 | 2     |

| 00            | 10                                                           | 01000                 | 3     |

| 01            | 00                                                           | 11000                 | 4     |

| 01            | 01                                                           | 01000                 | 5     |

| 10            | 00                                                           | 01000                 | 6     |

| 10            | 01                                                           | 01100                 | 7     |

| 10            | 10                                                           | 00110                 | 8     |

| 10            | 11                                                           | 00000                 | 9     |

| 11            | 00                                                           | 01100                 | 10    |

| 11            | 01                                                           | 00110                 | 11    |

| 11            | 10                                                           | 10001                 | 12    |

TABLE III Parameters of Mealy FSM S<sub>1</sub>

|                     | Р | PY | PY <sub>0</sub> | PYJ |

|---------------------|---|----|-----------------|-----|

| $n(\mathbf{P})$     | 8 | 6  | 5               | 5   |

| $n(\dot{R}\dot{G})$ | 3 | 3  | 3               | 3   |

| $n(\mathbf{Y})$     | 0 | 40 | 160             | 80  |

be formed, for example:

$$D_{3} = \overline{Q_{1}} \overline{Q_{2}} \overline{Q_{3}} \overline{x_{2}} + \overline{Q_{1}} Q_{2} \overline{Q_{3}} \overline{x_{2}} + Q_{1} \overline{Q_{2}} \overline{Q_{3}} \overline{x_{2}} \overline{x_{3}}$$

$$+ Q_{1} Q_{2} \overline{Q_{3}} \overline{x_{1}} \overline{x_{3}},$$

$$\psi_{2} = \overline{Q_{1}} \overline{Q_{2}} \overline{Q_{3}} \overline{x_{1}} x_{2} + \overline{Q_{1}} Q_{2} \overline{Q_{3}} \overline{x_{2}} + Q_{1} \overline{Q_{2}} \overline{Q_{3}} \overline{x_{2}} x_{3}$$

$$+ Q_{1} \overline{Q_{2}} Q_{3} \overline{x_{2}} \overline{x_{3}} + Q_{1} Q_{2} \overline{Q_{3}} \overline{x_{1}} x_{3}.$$

It can be noticed that these equations are not minimized ones. This proceed is not required at logic synthesis level because it would be preformed by third party synthesis & implementation tools in next step. This step finishes logic synthesis process. Now, the key parameters, like number of logic equations or number of memory bits, of logic circuit can be calculated. The Table III presents these parameters for FSM  $S_1$ , where

- n(P) is a number of logic equations implemented by the combinational circuit P,

- n(RG) is a number of D type flip-flops in the register RG,

- n(Y) is a number of used memory bits in the decoder Y.

```

www.journals.pan.pl

```

```

module S1_P (x, Q, psi, D);

input [1:3] x;

input [1:3] Q;

output [1:2] psi;

output [1:3] D;

assign psi[1]=~x[2] & ~Q[1] & ~Q[2] & ~Q[3]

| x[3] & Q[1] & ~Q[2] & Q[3]

| ~x[3] & Q[1] & ~Q[2] & Q[3]

| x[1] & Q[1] & Q[2] & ~Q[3];

...

assign D[3]=~x[2] & ~Q[1] & ~Q[2] & ~Q[3]

| ~x[2] & ~Q[1] & Q[2] & ~Q[3]

| ~x[2] & ~x[3] & Q[1] & ~Q[2] & ~Q[3]

| ~x[1] & ~x[3] & Q[1] & Q[2] & ~Q[3];

; endmodule

```

Fig. 8. Verilog description of combinational circuit P.

```

module S1_RG (clk, res, D, Q);

input clk, res;

input [1:3] D;

output [1:3] Q;

reg [1:3] Q;

always @(posedge clk or posedge res)

if (res)

Q <= 3'b0;

else

Q <= D;

endmodule</pre>

```

Fig. 9. Verilog description of register RG.

Now, the logic circuit can be prepared for implementation (step 8). First, the whole circuit is described in Verilog HDL. The combinational circuit P is described using continues assignment based on equations received in step 7 (Fig. 8). The register RG is described as 3-bits D type flip-flop with asynchronous reset signal and trigged by rising edge of clock signal (Fig. 9). There was used standard synthesis template [18], [19] for this purpose. The circuit Y is described with use of one process trigged by falling edge of the clock signal (Fig. 10). The content of the memory is described with use of case statement and it was taken from the table of decoder Y (Tab. II) that was received in step 6. There is also set special synthesis attribute bram map to yes to satisfy implementation into embedded memory blocks. This is attribute for Xilnix devices, and in case od different vendor devices it should be replaced by different one. Finally, the toplevel module is described as instantiation of already described components (Fig. 11). Their connections should be adequate to the logic structure presented in Figure 3. Now, such description can be passed into third party synthesis & implementation tools. In this case, there was used Xilnix ISE with XST, and the obtained results are shown in Table IV.

The application of this method with joined multiple encoding reduce the memory size by two and do not affect the number of implemented logic functions in comparison with well known method multiple encoding. The presented in Table III parameters of example FSM  $S_1$  shows this

```

module S1_Y (clk, psi, Q, y);

input clk;

input [1:2] psi;

input [1:2] Q;

output [1:5] y;

reg [1:5] y;

// synthesis attribute bram_map of S1_Y is

yes

always @(negedge clk)

case ({Q, psi})

4'b0000: y = 5'b10000;

4'b0011: y = 5'b11000;

4'b0010: y = 5'b01000;

...

endcase

endmodule

Fig. 10. Verilog description of decoder Y.

```

```

module S1 (clk, res, x, y);

input clk, res;

input [1:3] x;

output [1:5] y;

wire [1:3] d;

wire [1:3] q;

wire [1:2] psi;

S1_RG UD (.clk(clk), .res(res), .D(d),

.Q(q));

S1_P UP (.x(x), .Q(q),

.D(d), .psi(psi));

S1_Y UY (.clk(clk), .psi(psi), .Q(q[1:2]),

.y(y));

```

endmodule

Fig. 11. Verilog description of top-level module.

TABLE IV IMPLEMENTATION RESULTS OF MEALY FSM  $\ensuremath{\mathsf{S}}_1$

|        | Р  | PY | PY <sub>0</sub> | $PY_J$ |

|--------|----|----|-----------------|--------|

| Slices | 10 | 9  | 8               | 7      |

| LUTs   | 18 | 16 | 14              | 13     |

| FFs    | 3  | 3  | 3               | 3      |

| BRAMs  | -  | 1  | 1               | 1      |

dependence. Although, the implementation results depends also on functional decomposition of logic equations process and state encoding, and it cause that the number of utilized logic elements could change. It have to be mentioned that encoding of states for both synthesis method is different because the proposed method with joined multiple encoding required special state encoding algorithm. Additionally, the number of embedded memory blocks is the same for all synthesized structures because of small size of example FSM S<sub>1</sub>. In case of bigger examples, the value of n(Y) parameter has also influence on number of utilized embedded memory blocks.

# VI. SUMMARY

There was proposed method of synthesis and double-level structure of a digital device implementing an FSM. This structure is dedicated to presented synthesis method. The synthesis method is based on the multiple encoding of microinstructions of a state machine and structural decomposition of its logic circuit. This method was adapted for synthesis process into FPGA devices. It takes advantage of features of new FPGA devices like embedded memory blocks. The utilization of such resources leads to reduce the number of required standard logic blocks, like LUTs, for implementation of a control unit. The proposed method is also oriented on reduction of memory size.

#### References

- [1] S. I. Baranov, *Logic Synthesis for Control Automat*. Boston: Kluwer Academic Publishers, 1994.

- [2] A. Barkalov and L. Titarenko, *Logic Synthesis for FSM-based Control Units*, ser. Lecture Notes in Electrical Engineering. Berlin: Springer-Verlag, 2009, vol. 53.

- [3] Z. Salcic, VHDL and FPLDs in Digital Systems Design, Prototyping and Customization. Boston: Kluwer Academic Publishers, 1998.

- [4] H. Kubátová, "Finite state machine implementation in FPGAs," in Design of Embedded Control Systems, M. Adamski, A. Karatkevich, and M. Węgrzyn, Eds. New York: Springer, 2005, pp. 177–187.

- [5] J. Jenkins, *Designing with FPGAs and CPLDs*. Upper Saddle River, NJ: Prentice Hall, 1994.

- [6] C. Scholl, Functional Decomposition with Application to FPGA Synthesis. Boston: Kluwer Academic Publishers, 2001.

- [7] M. Rawski, H. Selvaraj, T. Łuba, and P. Szotkowski, "Application of symbolic functional decomposition concept in FSM implementation targeting FPGA devices," in *Proceedings of the 6th International Conference on Computational Intelligence and Multimedia Applications ICCIMA*'05, Las Vegas, NV, 2005, pp. 153–158.

- [8] G. Borowik, M. Rawski, G. abiak, A. Bukowiec, and H. Selvaraj, "Efficient logic controller design," in *Fifth International Conference* on Broadband and Biomedical Communications IB2Com'10, Malaga, Spain, 2010, pp. [CD–ROM].

- [9] M. Adamski and A. Barkalov, Architectural and Sequential Synthesis of Digital Devices. Zielona Góra: University of Zielona Góra Press, 2006.

- [10] A. Bukowiec and A. Barkalov, "Structural decomposition of finite state machines," *Electronics and Telecommunications Quarterly*, vol. Vol. 55, no. No. 2, pp. 243–267, 2009.

[11] A. Bukowiec, "Synthesis of Mealy FSM with multiple shared encoding

- [11] A. Bukowiec, "Synthesis of Mealy FSM with multiple shared encoding of microinstructions and internal states," in *Proceedings of IFAC Workshop on Programmable Devices and Embedded Systems PDeS'06*, Brno, Czech Republic, 2006, pp. 95–100.

- [12] —, "Architectural synthesis of FSMs with joined multiple encoding," *Electrical Review*, vol. Vol. 2011, no. No. 11, pp. 150–153, 2011.

- [13] A. Bukowiec, A. Barkalov, and L. Titarenko, "FSMs implementation into FPGAs with multiple encoding of states," in *Proceedings of IEEE East-West Design & Test Symposium EWDTS'08*. Lviv, Ukraine: IEEE, 2008, pp. 72–75.

- [14] E. F. Moore, "Gedanken-experiments on sequential machines," in Automata Studies, ser. Annals of Mathematical Studies, C. E. Shannon and J. McCarthy, Eds. Princeton, NJ: Princeton University Press, 1956, vol. 34, pp. 129–153.

- [15] G. H. Mealy, "A method for synthesizing sequential circuits," *Bell System Technical Journal*, vol. Vol. 34, no. No. 5, pp. 1045–1079, 1955.

- [16] S. Yang, "Logic Synthesis and Optimization Benchmarks User Guide. version 3.0." Microelectronics Center of North Carolina, Research Triangle Park, NC, Tech. Rep. 1991-IWLS-UG-Saeyang, 1991. [Online]. Available: http://jupiter3.csc.ncsu.edu/brglez/Cite-BibFiles-Reprintshome/Cite-BibFiles-Reprints-Central/BibValidateCentralDB/Cite-ForWebPosting/1991-IWLSUG-Saeyang/1991-IWLSUG-Saeyang guide.pdf

- [17] A. Bukowiec, Synthesis of Finite State Machines for FPGA devices based on Architectural Decomposition, ser. Lecture Notes in Control and Computer Science. Zielona Góra: University of Zielona Góra Press, 2009, vol. 13.

- [18] P. Eles, K. Kuchcinski, and Z. Peng, System Synthesis with VHDL. Norwell: Springer, 1998.

- [19] D. Thomas and P. Moorby, *The Verilog Hardware Description Language*, 5th ed. Norwell, MA: Kluwer Academic Publishers, 2002.